# SPECIAL ISSUE ARTICLE

# Mold Fabrication for 3D Dual Damascene Imprinting

S. M. Saydur Rahman · Bo Cui

Received: 11 September 2009/Accepted: 16 January 2010/Published online: 30 January 2010 © The Author(s) 2010. This article is published with open access at Springerlink.com

Abstract Previously, a damascene process based on nanoimprint lithography has been proposed (Schmid G M, et al. in J Vac Sci Technol B 24(3) 1283, 2006) to greatly reduce the fabrication steps of metal interconnection in integrated circuit. For such a process to become a viable technique, a mold having two pattern levels with precise alignment between them must be fabricated first. To this end, this work demonstrates a "self-aligned" fabrication process where the two pattern levels would be perfectly aligned if ignoring the noise during e-beam writing. The process is based on one EBL on a bi-layer resist stack, with the sensitivity for the top layer much higher than that of the bottom layer, which enables separate pattern transfer of the two pattern levels. Using ZEP-520A and poly(dimethylglutarimide) (PMGI) resists, we fabricated pillars having a diameter of 150 nm sitting on ridges having a width of 1.5 µm, which can be used to create via-holes and trenches for IC interconnect by nanoimprint lithography. The current process can also find applications in other areas that require two-level patterning with precise alignment between them.

**Keywords** Nanofabrication · Electron beam lithography · Nanoimprint lithography · Mold · Nanostructure · Resist

## Introduction

An advanced integrated circuit (IC) typically has eight or more wiring levels, each of which consists of metal via and line structures. The metal lines distribute signals within each interconnect level, whereas metal vias transmit signals between the adjacent wiring levels. In state-of-the-art ICs, copper is used as the interconnect material due to its higher conductivity than Al. Owing to the lack of a well-established plasma etching process for Cu, dual damascene process is adopted to fabricate Cu interconnect except for the first wiring level where tungsten CVD plug is used. In a dual damascene process, in order to significantly reduce the process steps, vias and lines are fabricated simultaneously by Cu electroplating and chemical mechanical polishing. However, it still needs more than twenty process steps to fabricate each wiring level using dual damascene process [1].

In a recent work, Schmid et al. [2] proposed a damascene process based on imprint lithography to fabricate metal interconnect. Via-holes and trenches are created in a single imprint step using a mold having two pattern levels consisting of pillars sitting on top of ridges. When imprintable dielectric material is used as a UV-curable imprint resist, the number of steps of such a process is only one-third that of the standard photolithography-based dual damascene process. However, for the imprint damascene process to become a practical manufacturing method, onefirst needs to fabricate a 3D imprint mold (template) with acceptable overlay error between the two pattern levels. This is not trivial because, unlike projection optical lithography where  $4 \times$  reduction is used, imprint is a  $1 \times$  process where the overlay error in the mold will be transferred to the resist without any error reduction.

The mold in Ref. [2] has been fabricated by electron beam lithography (EBL) with two resist exposures for the

S. M. Saydur Rahman · B. Cui (🖂)

Department of Electrical and Computer Engineering, Waterloo Institute for Nanotechnology, University of Waterloo, Waterloo, ON N2L3G1, Canada e-mail: bcui@uwaterloo.ca

two pattern levels. In this work, we will demonstrate a mold fabrication technique by EBL where the two levels of mold structures are exposed in the same step using a bi-layer resist stack having different sensitivities. The structures are therefore "self-aligned" with each other with negligible overlay error. In addition to improved alignment accuracy, the process consists of fewer steps than previous mold fabrication process that involves two EBL steps and two pattern transfer steps by etching. Moreover, in the previous process, the resist for the second pattern level is spun on a non-flat surface consisting of features of the first pattern level, which leads to resist film thickness nonuniformity and process error unless a dry evaporated resist is used [3, 4]. This problem is not an issue for the current process since the bi-layer resists are spun on a flat wafer surface one after the other. Besides semiconductor device interconnect, the current method can be extended to other applications requiring two-level patterning with precise alignment between them.

## **Bi-Layer EBL Resist**

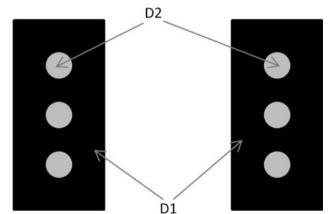

The mold for the imprint damascene process has two pattern levels consisting of pillars sitting on top of ridges, which is fabricated here by EBL using a bi-layer resist with the top layer (that defines the metal lines) more sensitive than the bottom one (that defines the metal vias). The exposure dose distribution is shown in Fig. 1, with dose D1 high enough to result in full development of the top resist layer, yet low enough to avoid significant development of the bottom resist layer; and dose D2 high enough to result in full development of the bottom resist layer. Because D2 is much higher than D1, the top layer would be greatly overexposed at the pillar locations. However, this is not problematic here, and the edge of the ridge is still well

Fig. 1 Dose distribution for e-beam exposure of the bi-layer resist stack, with the dose D2 substantially higher than D1

defined by the exposure D1, as the pillar diameter is much smaller than the ridge width and thus the edge of the ridge receives little exposure due to backscattered electrons from exposure D2 at the pillar locations. Besides sensitivity, another critical requirement for the two resists is that the solvent used to dissolve the top layer for spin-coating and metal liftoff should not attack the bottom resist.

Here we have chosen the resist combination as ZEP-520A (from Zeon Corp.) with sensitivity  $\sim 50 \ \mu\text{C/cm}^2$  for the top layer, and poly(dimethylglutarimide) (PMGI, from MicroChem Corp.) with sensitivity  $\sim 1,000 \ \mu\text{C/cm}^2$  for the bottom layer. In addition to the large difference in sensitivity, ZEP-520A can be dissolved by anisole for metal liftoff, which does not attack the bottom PMGI layer. PMGI is not a typical EBL resist. Instead, it is commonly used as a liftoff resist in a bi-layer stack with PMGI as the bottom layer [5], because its chemistry is "orthogonal" to that of common EBL resist like ZEP-520A (and PMMA): on the one hand, it is resistant to most solvents that dissolve ZEP-520A, which is essential for spin-coating the bi-layer resist stack; on the other hand, it is dissolved (etched laterally when underneath ZEP-520A) by base solutions consisting of KOH or tetramethylammonium hydroxide (TMAH), which does not attack the top ZEP-520A layer. As the dissolution rate by a base solution increases drastically when PMGI is exposed to electrons, it is effectively an EBL resist with sensitivity of 50–100  $\mu$ C/cm<sup>2</sup> [6, 7]. However, its sensitivity drops considerably to  $\sim 1,000$  $\mu$ C/cm<sup>2</sup> when using solvent developers such as methyl ethyl ketone (MEK) and methyl isobutyl ketone (MIBK) [8], making it a suitable choice for the current bi-layer resist process. The rather low sensitivity of PMGI does not increase the e-beam writing time significantly because the exposure area of the pillars is much less than that of the trenches.

#### **Process for Nanoimprint Mold Fabrication and Results**

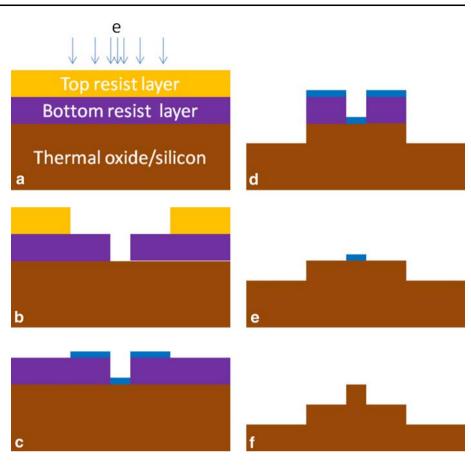

The fabrication process is illustrated in Fig. 2. Both resists were spun at 2,000 rpm for 40 s., leading to a film thickness of 70 nm for PMGI and 100 nm for ZEP-520A (the as-purchased resist was 1:1 diluted by anisole to achieve this thickness). After spin-coating, PMGI was baked at 200°C for 10 min on a hotplate before coating ZEP-520A that was subsequently baked using the same condition. Exposure of the bi-layer resist was performed using a LEO-1530 field emission SEM equipped with a Nabity nanometer pattern generation system (NPGS). The acceleration voltage was fixed at 20 kV, and the beam current was 360 pA (aperture 30  $\mu$ m). After exposure, ZEP-520A resist was developed using xylene (o-,m-,p- mixed) for 20 s; and PMGI was developed using MEK:ethanol = 26.5:73.5 for

Fig. 2 Fabrication steps for a mold having two pattern levels for imprint damascene process. **a** e-beam exposure; **b** develop the *top* and *bottom* resist layers; **c** Cr evaporation and liftoff by dissolving the top resist layer; **d** RIE etch bottom resist layer and SiO<sub>2</sub>; **e** liftoff Cr by dissolving the bottom resist layer; **f** RIE SiO<sub>2</sub> and remove Cr

10 s. A 15 s. rinse by 2-proponol is carried out after each development. A 25 nm Cr was then deposited using e-beam evaporation on the resist stack that consists of holes

in the bottom layer and trenches in the top layer. Liftoff of the Cr pattern in the top resist layer was obtained by soaking the wafer in anisole for 10 min, then adding

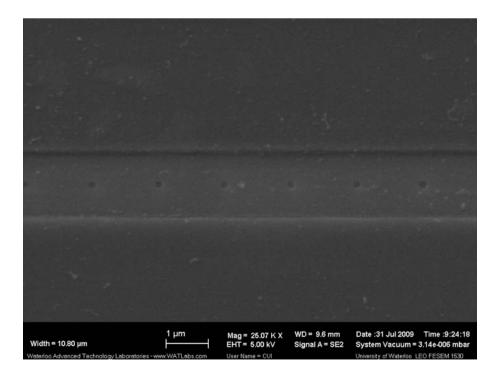

Fig. 3 Developed pattern in the bi-layer resist stack of ZEP-520A/PMGI, whose profile corresponds to Fig. 2b ultrasonic agitation for 2 min. Next, the PMGI is etched using oxygen reactive ion etching (RIE) with the Cr as etching mask, followed by thermal oxide RIE using a Phantom II ICP-RIE. The oxide etching is carried out using a gas mixture of 30 sccm CF<sub>4</sub> and 5 sccm Ar with a RIE power of 100 W (no ICP power) and a pressure of 20 mTorr, which resulted in an etching rate of 60 nm/min for SiO<sub>2</sub> and ~1.5 nm/min for Cr (selectivity ~1:40). Liftoff of Cr on the bottom resist layer was carried out by soaking the wafer in MF-319 (a photolithography developer containing 0.24 M TMAH, from MicroChem Corp.) for 5 min. Finally, the pillars were etched by RIE using the same recipe as above, and the remaining Cr was removed by wet etching using an etchant containing a mixture of 120 g Ceric ammonium nitrate (Ce(NH<sub>4</sub>)<sub>2</sub>(NO<sub>3</sub>)<sub>6</sub>), 100 ml acetic acid (CH<sub>3</sub>COOH) and 500 ml deionized water.

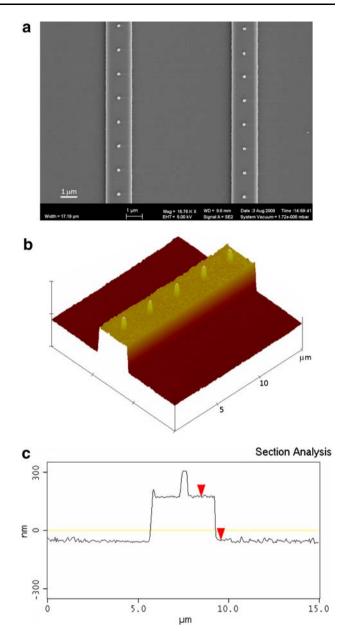

Figure 3 shows scanning electron microscope (SEM) image of the two-level resist pattern after development of the ZEP-520A by xylene and PMGI by MEK; and Fig. 4 shows the SEM and atomic force microscope (AFM) images of the completed mold. The dimension of the pillars is 150 nm in diameter and 125 nm in height; and that of the ridge is about 1.5  $\mu$ m in width and 225 nm in depth. Since there is no hard etching mask (Cr) on the ridge during the RIE of pillars, the ridges would shrink for order 10 nm depending on the etched depth. As both PMGI (using solvent developers) and ZEP-520A are high-resolution resists with high contrasts [8, 9], smaller features could be fabricated using the current process.

## Discussion

Compared to the previous process for the fabrication of an imprint mold having two pattern levels, which involves two EBL steps, two metal liftoffs, and two etchings, the current process consists of only one EBL step, one metal liftoff, and two etchings; thus, it greatly reduces the mold fabrication cost and increases the throughput at the same time. In addition, using one EBL step on a bi-layer resist stack, a more straightforward fabrication procedure would consist of (after EBL) developing the top layer, metal deposition and liftoff, and RIE to define the ridge pattern; removing the metal and repeating the process steps to define the pillar pattern. Such a process involves two metal depositions and liftoffs, whereas the current one contains only one metal deposition step, so is simpler. It can achieve the desired result because SiO<sub>2</sub> etching using CF<sub>4</sub> gas is highly anisotropic, leading to negligible etch of the SiO<sub>2</sub> surrounding the Cr "disk" on the substrate. Otherwise, a more isotropic etching chemistry using SF<sub>6</sub> gas would result in a ring-shaped pattern surrounding the Cr "disk" [10].

**Fig. 4** AFM and SEM images of the completed mold having two pattern levels for imprint damascene process. **a** SEM image; **b** 3D AFM image; **c** AFM profile showing the height of the pillars and ridges

For the resist selection, we have used two positive resists ZEP-520A and PMGI. Resist combination of PMMA and PMGI could also be used to fabricate the mold, yet the process window would be narrower since the sensitivity difference between PMMA and PMGI is smaller. In addition, acetone, the most common solvent for liftoff, cannot be used here because it was found that PMGI can be dissolved by acetone once it is exposed to electrons with the dissolution rate depending on the exposure dose. Therefore, we have chosen anisole for Cr liftoff, which was found not to attack PMGI noticeably even when it is exposed to electrons. Lastly, besides positive resist combinations, in principle, one can also use negative resists (one negative and one positive, or both negative) by carrying out the pattern transfer using RIE with the resist as etching mask. Such a process involves fewer steps as no metal deposition and liftoff is needed, though the process would be limited by the etching selectivity between the resist and SiO<sub>2</sub>.

Finally, though we have succeeded in fabricating the mold having two pattern levels, the current process is not expected to be able to completely replace the conventional process involving two EBL steps. For instance, it would be difficult using the current process to fabricate a two-level structure where the top (fine) features are not located far away from the edge of the bottom (large) features, as otherwise the edge would be overexposed due to proximity effect that results in a poorly defined feature edge. The current process is also not capable of fabricating a two-level structure where the features of the "top" level sit inside the trenches (rather than on top of the ridges) of the "bottom" level. Such a structure can only be fabricated using the conventional method involving two separate EBL steps, as demonstrated in Ref [4].

## Conclusions

We have demonstrated the fabrication of nanoimprint lithography molds having two pattern levels that can be used for the patterning of via-holes and trenches for IC interconnection. The process involves only one EBL step on a bi-layer resist stack, so the alignment between the two levels would be perfect if ignoring the noise during e-beam writing. For such a process to work properly, the two resists must have very different sensitivity; and their chemistry should be ideally "orthogonal"—the liquid (solvent or aqueous solution) that dissolves one resist should not attack the other resist. Using ZEP-520A and PMGI as the top and bottom layer resists, we fabricated an imprint mold consisting of 150-nm diameter pillars sitting on top of 1.5  $\mu$ m—wide ridges. Other resist combinations, including negative resists, may also be used for the fabrication. The current process can be extended to other applications requiring two-level patterning with precise alignment between them.

**Open Access** This article is distributed under the terms of the Creative Commons Attribution Noncommercial License which permits any noncommercial use, distribution, and reproduction in any medium, provided the original author(s) and source are credited.

#### References

- 1. MacDonald S, Hughes G, Proc SPIE 5992 59922F (2005)

- G.M. Schmid, M.D. Stewart, J. Wetzel, F. Palmieri, J. Hao, Y. Nishimura, K. Jen, E.K. Kim, D.J. Resnick, J.A. Liddle, C.G. Willson, J. Vac. Sci. Technol. B 24(3), 1283 (2006)

- P.S. Kelkar, J. Beauvais, E. Lavallee, D. Drouin, M. Cloutier, D. Turcotte, P. Yang, K.M. Lau, R. Legario, Y. Awad, V. Aimez, J. Vac. Sci. Technol. A 22(3), 743 (2004)

- J. Beauvais, E. Lavallee, A. Zanzal, D. Drouin, K.M. Lau, T. Veres, B. Cui, Proc. SPIE 5751, 392 (2005)

- 5. Y. Chen, K. Peng, Z. Cui, Microelectro. Eng. 73-74, 278 (2004)

- H. Takano, H. Nakano, H. Minami, K. Hosogi, N. Yoshida, K. Sato, Y. Hirose, N. Tsubouchi, J. Vac. Sci. Technol. B 14(6), 3483 (1996)

- B. Cord, C. Dames, K.K. Berggren, J. Aumentado, J. Vac. Sci. Technol. B 24(6), 3139 (2006)

- 8. B. Cui, T. Veres, Microelectro. Eng. 85, 810 (2008)

- 9. L.E. Ocola, A. Stein, J. Vac. Sci. Technol. B 24(6), 3061 (2006)

- 10. B. Cui, T. Veres, Microelectron. Eng. 84, 1544 (2007)