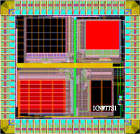

IC Tape-out History

22.ICSWTTS2

Date: March 9, 2012

Design Team: Tahseen Shakir

Technology: TSMC CMOS 65nm

Package: CFP80

CMC Run: 1201CS

Chip Details:

- A 32 Kbit SRAM macro array with conventional 6T cells and novel timing insensitive, wirte-back sense amplifiers and a proposed programmable WL boos driver.

- A 32 Kbit SRAM macro utilizes a novel 5T SRAM bitcell with a single ended sensing scheme.

21.ICSWTPC2

Date: March 9, 2011

Design Team: Pierce Chuang

Technology: TSMC CMOS 65nm

Package: CFP68

CMC Run: 1101CS

Chip Details:

- A 64bit Adder with Constant-Delay Logic.

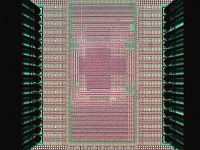

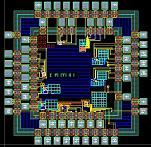

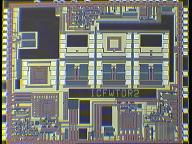

21.ICFWTJS2

Date: February 10th, 2010

Design Team: Jaspal Singh Shah, David Li, Adam Neale

Technology: TSMC CMOS 180nm

Package: CFP80

CMC Run: 1001CF

Chip Details:

- Novel access architecture for SRAM

- Metastability testing and analysis of high performance flip flops

- Flexible SRAM timing control scheme

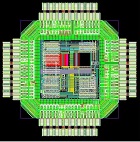

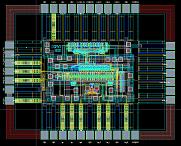

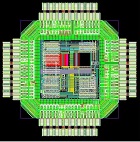

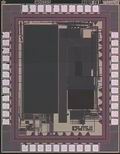

20.ICNWTTS1

Date:

November 18th, 2009

Design Team: Tahseen Shakir, Jaspal Singh Shah,

David Rennie

Technology: STM CMOS 65nm

Package: 68CQFP

CMC Run: 0903CN

Chip Details:

- 32kb low power, high

performance 5T SRAM

- 32kb low power, high

performance 9T SRAM

- 32kb soft error

robust 8T SRAM with novel access architecture

- 32kb

conventional 6T

reference SRAM

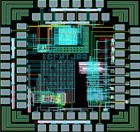

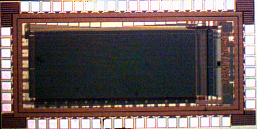

19.ICNWTPC1

Date:

November 18th, 2009

Design Team: Pierce Chuang, David Li, Adam

Neale

Technology: STM CMOS 65nm

Package: 68CQFP

CMC Run: 0903CN

Chip Details:

- High

performance 64-bit adder with dynamic-feedthrough logic

- 2kb,

soft-error robust high performance 2R1W register file

- High

performance single and dual-supply flip-flops with novel pre-discharge

and positive feedback

scheme

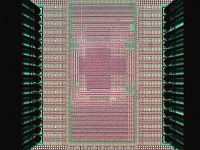

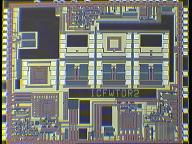

18. ICNWTJS1

Date:

September 24th, 2008

Design Team: Shah Jahinuzzaman, Tasreen

Charania, Hossein Sharbishaei, Tahseen Shakir,Jaspal Shah

Technology: STM CMOS 65nm

Package: 64CQFP

CMC Run: 0803CN

Chip Details:

- Arrays of flip-flops

to measure the soft-error tolerance of various flip-flop architectures

- New SRAM

architectures optimized for power and area

- ESD circuits aimed at

providing protection against various kinds of ESD events with a low

parasitic load

- Circuit designed to

dynamically measure the ripple of the supply voltage

17. ICLWTSA2

Date:

July 4th, 2007

Design Team: Shah Jahinuzzaman, Mohammad

Sharifkhani, Hossein Sharbishaei, Tahseen Shakir, Sumanjit Lubana,

Jaspal Shah

Technology: STM CMOS 90nm

Package: 64CQFP

CMC Run: 0703CL

Chip Details:

- 64kb ultra low-power

SRAM with error correction code (ECC) circuits

- 32kb SRAM with

soft-error tolerant cell architecture

- 32kb SRAM with novel

cell architecture

16. ICLWTSA1

Date:

January 10th, 2007

Design Team: Shahab Ardalan, Mohammad

Sharifkhani, Shah M. Jahinuzzaman

Technology: STM CMOS 90nm

Package: 68PGA

CMC Run: 0701CL

Chip Details:

- 4 Gbps ultra

low-power clock and data recovery circuit

- Low-power SRAM with

novel cell architecture

- High performance soft

error robust flip-flops

15. ICFWTSJ1

Date:

November 29th, 2006

Design Team: Shah M. Jahinuzzaman, Mohammad

Sharifkhani

Technology: TSMC CMOS 0.18 micron

Package: 44CQFP

CMC Run: 0604CF

Chip Details:

- 128b error correction

circuit (ECC) for soft error mitigation in low-power SRAMs

- Low-power SRAM array

with novel sensing scheme

14. ICGWTAP1

Date:

March 9th, 2005

Design Team: Andrei Pavlov, Mohammad

Sharifkhani

Technology: IBM CMOS 0.13 micron

Package: TBD

CMC Run: 0501CG

Chip Details:

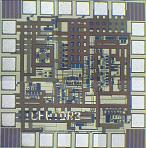

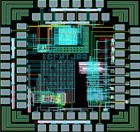

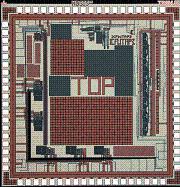

13. ICFWTNM1

Date:

November 3rd, 2004

Design Team: Nitin Mohan, Wilson Fung, Derek

Wright

Technology: TSMC CMOS 0.18 micron

Package: CFP 80

CMC Run: 0404CF

Chip Details:

- A complete 20Kb TCAM

chip with priority encoder and test circuitry

- Three novel match

line sense amplifiers

- Novel design of

priority encoder

- Total on-chip

decoupling capacitance is approximately 1 nF

- Total transistor

count (excluding decoupling capacitors) is approximately 400K

12. ICFWTFD1

Date:

November 3rd, 2004

Design Team: Mohammad Sharifkhani

Technology: TSMC CMOS 0.18 micron

Package: CFP 24

CMC Run: 0404CF

Chip Details:

- An oversampling

second order phase domain frequency digitizer operating at 128 MHz for

Bluetooth applications

11. ICFWTBPC

Date:

May 26th, 2004

Design Team: Bhaskar Chatterjee, Mohammad

Maymandi-Nejad

Technology: TSMC CMOS 0.18 micron

Package: CFP 80

CMC Run: 0402CF

Chip Details:

- Dual supply CPL based

32-bit ALU (17k transistors) with energy reduction and built-in DFT

scheme to detect delay faults with resolution greater than 60ps

- Uses dual supply

latching scheme to interface signals and maintain dual supply operation

without static power

10. ICFWTMMG

Date:

May 26th, 2004

Design Team: Mohamed Elgebaly

Technology: TSMC CMOS 0.18 micron

Package: 44 CQFP (Surface Mount)

CMC Run: 0402CF

Chip Details:

- A critical path

emulator which closely tracks the actual on-chip critical path at any

given condition

- The new architecture

recovers most of the safety margin required by conventional Dynamic

Voltage Scaling (DVS) systems

- The technique is

applied to a 16x16-bit multiplier

9. ICFWTWF1

Date:

May 26th, 2004

Design Team: Wilson W. Fung, Shahrzad Naraghi

Technology: TSMC CMOS 0.18 micron

Package: 44 CQFP (Surface Mount)

CMC Run: 0402CF

Chip Details:

- A novel

high-performance priority encoder (256-bit) for CAM/TCAM memory (faster

priority resolution)

- A modified

current-race sensing scheme for multiple match detection in CAM/TCAM

(faster sensing time and lower energy consumption)

- A high-performance

ALU design-for-test circuit for state-of-the-art microprocessor

8. ICFWTKTC

Date:

May 26th, 2004

Design Team: Christine Kwong, Shahrzad

Naraghi,

Bhaskar Chatterjee

Technology: TSMC CMOS 0.18 micron

Package: 44 CQFP

CMC Run: 0402CF

Chip Details:

- Test structures

pertaining to a Register Files containing leakage control techniques on

the WL drivers and Local bitlines for low power operation while

maintaining robust scaling

- A new single ended

interrupted-feedback register file memory cell that has lower switching

and leakage energy compared to the conventional ones

- CDL logic gates for a

32-bit adder using dual supply techniques for low power operation while

imporving performance

7. ICFWTMM2

Date:

February 4th, 2004

Design Team: Mohammad Maymandi-Nejad, Shahab

Ardalan, Igor Lovich

Technology: TSMC CMOS 0.18 micron

Package: CFP 80

CMC Run: 0401CF

Chip Details:

- A new low voltage DC

voltage regulator

- A novel temperature

compensated current source

- Timing control block

for a bio-implantable circuit

6. ICFWTNES

Date:

February 4th, 2004

Design Team: Muhammad Nummer

Technology: TSMC CMOS 0.18 micron

Package: CFP 80

CMC Run: 0401CF

Chip Details:

- A methodology for

testing high-performance pipelined circuits with slow-speed testers

- A clock timing

circuit controls pipelined data transfer in the test mode

- The clock timing

circuit capable of achieving a timing resolution of 50ps

- The design provides

the ability to test the clock timing circuit itself

5. ICFWTDR3

Date:

November 19th, 2003

Design Team: Dave Rennie

Technology: TSMC CMOS 0.18 micron

Package: 80 CFP

CMC Run: 0304CF

Chip Details:

- A 5 Gbit/s CDR

circuit using a linear phase detector with digital calibration

circuitry to correct for static phase offsets

4. ICFWTAP3

Date:

August 6th, 2003

Design Team: Andrei Pavlov, Nitin Mohan,

Wilson

W. Fung

Technology: TSMC CMOS 0.18 micron

Package: 84 PGA (Through-hole)

CMC Run: 0303CF

Chip Details:

3. ICFWTDR2

Date:

March 26th, 2003

Design Team: Dave Rennie, Mohammad

Maymandi-Nejad, Nitin Mohan

Technology: TSMC CMOS 0.18 micron

Package: 80 CFP (Surface-mount)

CMC Run: 0301CF

Chip Details:

- Two 5Gbit/s CDR

circuits: one with a linear phase detector, the other with a binary

phase detector

- A low voltage VCO

- An SC amplifier

- A novel static

Ternary Content Addressable Memory (TCAM) cell for low-energy and

high-performance parallel table lookups

2. ICFWTMM1

![[Coming soon]](../chip/ICFWTMM1_1.jpg)

Date:

November 20th, 2002

Design Team: Mohammad Maymandi-Nejad

Technology: TSMC CMOS 0.18 micron

Package: CFP 80

CMC Run: 0206CF

Chip Details:

- A sub 1-V opamp with

a novel CMFB circuit

- A novel digitally

programmable delay element

- A novel low voltage

1-bit quantizer

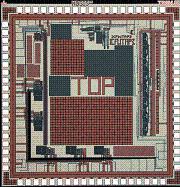

1. ICFWTSD1

Date: January 23rd, 2002

Design Team: Stephen Docking

Technology: TSMC CMOS 0.18 micron

Package: CFP 80

CMC Run: 0201CF

Chip Details:

- Designed to confirm the dependence of oscillation

frequency on different parameters as derived by the designer

- 5 ring oscillators with different number of delay

stages (3, 4, 5, 6, and 8 stages) to see how the frequency varied with

the number of stages

- The chip also has external controls to vary the

swing

and the tail current to see how the frequency varies with those

parameters

[Top]

![[Coming soon]](../chip/ICFWTMM1_1.jpg)