# E&CE 223 Digital Circuits & Systems

# Lecture Transparencies (Asynchronous Sequential Circuits)

## M. Sachdev

Department of Electrical & Computer Engineering, University of Waterloo

■ E&CE 223 ■

Department of Electrical & Computer Engineering, University of Waterloo

222 of 243

Department of Electrical & Computer Engineering, University of Waterloo

224 of 243

Department of Electrical & Computer Engineering, University of Waterloo

226 of 243

#### ■ E&CE 223 ■

## ■ E&CE 223 ■

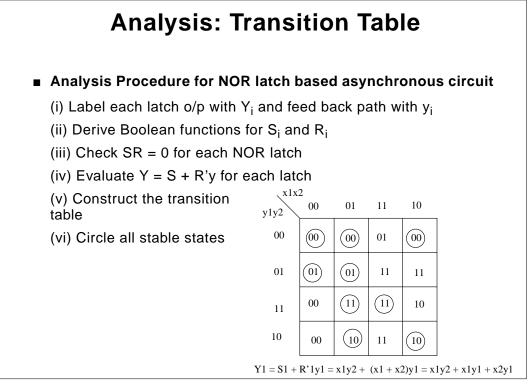

$\label{eq:2.1} Y_{\text{L}2} = S2 + R'2y2 = x1x2 + (x2 + y'1)y2 = x1x2 + x2y2 + y_2^2 \text{L}y_2^2 + y_2^2 + y_2^2 + y_2^2 \text{L}y_2^2 + y_2^2 + y_2^2 + y_2^2 \text{L}y_2^2 + y_2^2 + y_2^$

# **Design Example**

E&CE 223 🔳

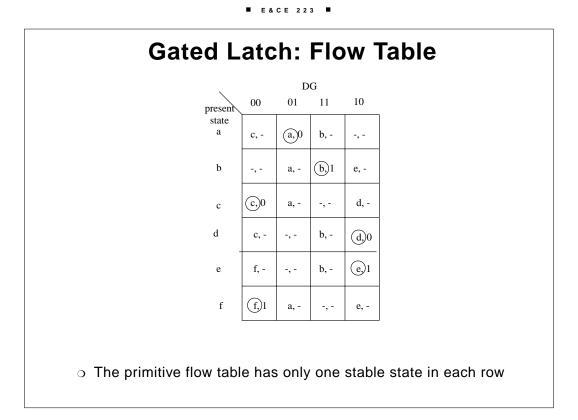

## To design a gated latch

• D, data input; G, gating input; Q, the output

.

$\circ$  Q <-- D if G = 1 and Q retains its previous value if G = 0

### Gated latch state table

| state | Inputs |   | Output | Comments           |

|-------|--------|---|--------|--------------------|

|       | D      | G | Q      |                    |

| а     | 0      | 1 | 0      | G = 1              |

| b     | 1      | 1 | 1      | G = 1              |

| С     | 0      | 0 | 0      | after state a or d |

| d     | 1      | 0 | 0      | after state c      |

| е     | 1      | 0 | 1      | after state b or f |

| f     | 0      | 0 | 1      | after state e      |

|       |        |   |        |                    |

Department of Electrical & Computer Engineering, University of Waterloo

234 of 243

#### ■ E&CE 223 ■

E&CE 223 🔳

.

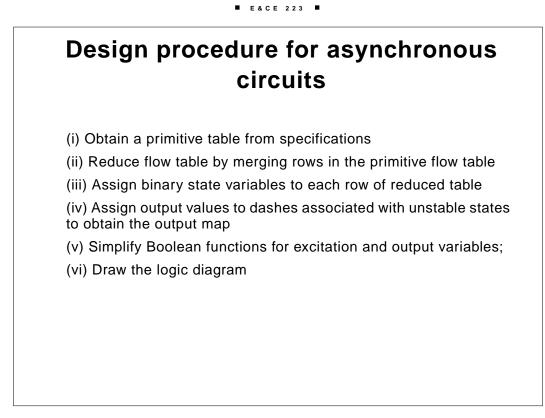

# Systematic reduction of Flow and State Tables

■ E&CE 223 ■

## Two techniques:

- o (i) Implications table, and

- o (ii) Merger diagram

### Implication table

- Tabulation of possible equivalent states (rows)

- o Tick for equivalent, and X for not equivalent

- o Two states, a, b are equivalent iff

(i) outputs are equivalent

(ii) transfers to the same (or equivalent state(s) for given input sequence

Department of Electrical & Computer Engineering, University of Waterloo

■ E&CE 223 ■

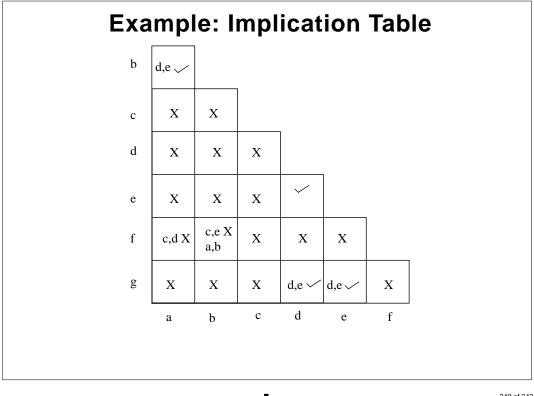

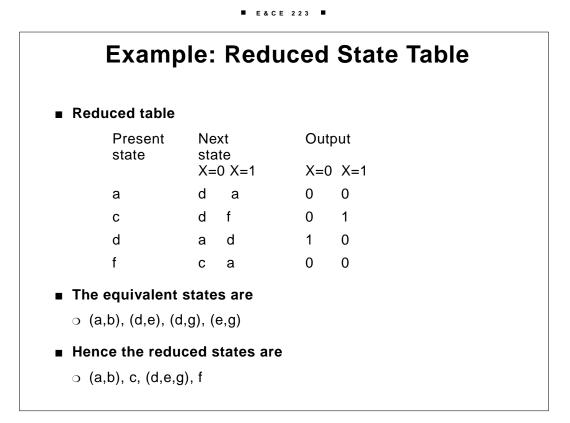

| Example: Implication Table |           |               |      |     |  |  |  |  |

|----------------------------|-----------|---------------|------|-----|--|--|--|--|

| State table to be reduced  |           |               |      |     |  |  |  |  |

| Present                    | Next      |               | Outp | but |  |  |  |  |

| state                      | sta<br>X= | ate<br>:0 X=1 | X=0  | X=1 |  |  |  |  |

| а                          | d         | b             | 0    | 0   |  |  |  |  |

| b                          | е         | а             | 0    | 0   |  |  |  |  |

| С                          | g         | f             | 0    | 1   |  |  |  |  |

| d                          | а         | d             | 1    | 0   |  |  |  |  |

| е                          | а         | d             | 1    | 0   |  |  |  |  |

| f                          | С         | b             | 0    | 0   |  |  |  |  |

| g                          | а         | е             | 1    | 0   |  |  |  |  |

|                            |           |               |      |     |  |  |  |  |

|                            |           |               |      |     |  |  |  |  |

|                            |           |               |      |     |  |  |  |  |

#### ■ E&CE 223 ■

Department of Electrical & Computer Engineering, University of Waterloo

#### ■ E&CE 223 ■