# University of Waterloo Department of Electrical & Computer Engineering E&CE 223 Digital Circuits and Systems

# Solution for Final Examination April 5, 2004

| Student Name: |    |    | Student | t ID: |       |

|---------------|----|----|---------|-------|-------|

| 1.            | 2. | 3. |         | 4.    | 5.    |

| 6.            | 7. | 8. |         | 9.    | Total |

## Total Time = 3 hours, Total Marks = 100

Attempt all problems. Show all work. If information appears to be missing make a reasonable assumption, state it, and proceed. Calculators are not needed and are not allowed.

## Problem 1 [10 Marks]

A) What is noise margin in digital logic gates? Explain briefly. [2]

Noise margin is the minimum external noise voltage that causes an undesirable change in the circuit output.

**B**) A smart engineer designed a 3 input NOR gate with **negative logic**, however he/she has trouble devising its truth table. You are expected to help him/her realize the truth table. [4]

| Inputs | Output |

|--------|--------|

| ABC    | Z      |

| 000    | 1      |

| 001    | 1      |

| 010    | 1      |

| 011    | 1      |

| 100    | 1      |

| 101    | 1      |

| 110    | 1      |

| 111    | 0      |

C) What is a race condition in asynchronous sequential circuits? Give an example of non-critical race condition. [2+2]

A race condition is said to exist in an asynchronous sequential circuit when two or more binary state variable change value in response to <u>a change in an input</u> <u>variable.</u>

If the final stable state that the circuit reaches dose not depend on the order in which the state variable change, the race is called a non-critical race.

## Problem 2 [12 marks]

A design engineer devised a new code, *Mycode*, to represent the decimal numbers. You are required to design a combinational circuit that converts a number represented in *Mycode* to BCD.

| Decimal<br>number | Mycode<br>ABCD | BCD #<br>EFGH |

|-------------------|----------------|---------------|

| 0                 | 0000           | 0000          |

| 1                 | 0011           | 0001          |

| 2                 | 0101           | 0010          |

| 3                 | 0110           | 0011          |

| 4                 | 1010           | 0100          |

| 5                 | 1011           | 0101          |

| 6                 | 1100           | 0110          |

| 7                 | 1101           | 0111          |

| 8                 | 1110           | 1000          |

| 9                 | 1111           | 1001          |

E = ABC

С

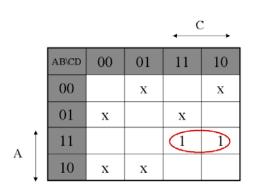

|   | AB\CD | 00 | 01 | 11 | 10 |

|---|-------|----|----|----|----|

|   | 00    |    | х  |    | х  |

|   | 01    | x  |    | x  |    |

| Î | 11    | 1  | 1  |    |    |

| ļ | 10    | X  | x  | 1  |    |

А

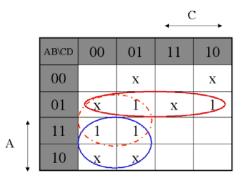

, C AB\CD 00 01 11 10 1 00 х Х 01 1 х х 1 1 11 А 10 1 х x

$\mathbf{H} = \mathbf{A}\mathbf{D} + \mathbf{A'C}$

### Problem 3 [12 marks]

A) For a carry look-ahead adder, redefine the carry propagate and carry generate as follow:

$P_i = A_i + B_i$ ; and  $G_i = A_i B_i$ Show that the output carry and the sum of a full adder becomes  $C_{i+1} = (C_i^{\prime}G_i^{\prime} + P_i^{\prime})^{\prime} = G_i + P_i C_i$ ; and  $S_i = (P_i G_i^{\prime})C_i^{\prime} + (P_i G_i)^{\prime}C_i$ . [6]

$(C_{i}' G_{i}' + P_{i}')' = (C_{i} + G_{i}). P_{i}$ =  $C_{i} P_{i} + G_{i} P_{i}$ =  $A_{i} B_{i} (A_{i} + B_{i}) + P_{i} C_{i}$ =  $A_{i} B_{i} + P_{i} C_{i}$ =  $G_{i} + P_{i} C_{i}$ =  $A_{i} B_{i} + (A_{i} + B_{i})C_{i}$ =  $A_{i} B_{i} + A_{i} C_{i} + B_{i} C_{i} = C_{i+1}$

$$\begin{split} (P_iG_i') \oplus C_i &= (A_i + B_i \ ) \ (A_i \ B_i \ )' \oplus C_i \\ &= \ (A_i + B_i \ ) \ (A_i' + B_i') \oplus C_i \\ &= (A_i' \ B_i + A_i \ B_i' \ ) \oplus C_i \\ &= A_i \oplus B_i \oplus C_i = S_i \end{split}$$

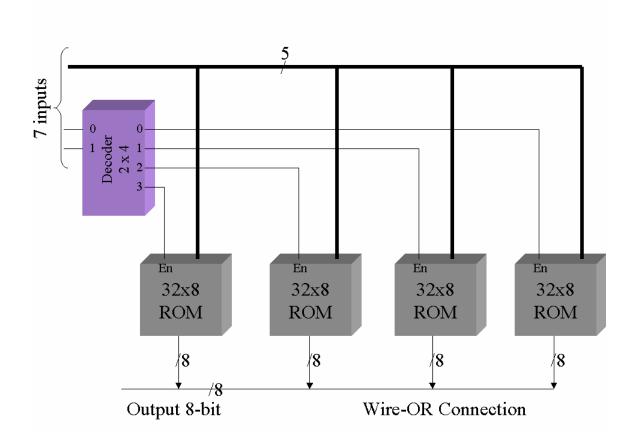

**B**) Given a 32x8 ROM chip with an enable input, show the block level required connections to construct a 128x8 ROM with 4 ROM chips and a decoder. [6]

## Problem 4 [10 marks]

Design a 4-input priority encoder with inputs and outputs as described in the table below. Please note that the input D0 has highest priority and D3 has lowest priority.

|    | Inp | outs |    |   | Outputs |   |

|----|-----|------|----|---|---------|---|

| D3 | D2  | D1   | DO | X | Y       | V |

| 0  | 0   | 0    | 0  | Х | Х       | 0 |

| 1  | 0   | 0    | 0  | 0 | 0       | 1 |

| Х  | 1   | 0    | 0  | 0 | 1       | 1 |

| X  | X   | 1    | 0  | 1 | 0       | 0 |

| Х  | Х   | Х    | 1  | 1 | 1       | 1 |

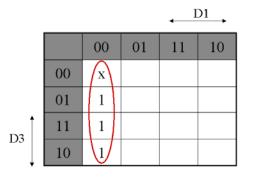

$x = D_0' D_1'$

D1 00 01 11 10 x (1)00 01 1 1 11 D3 1) 1 10

$$\begin{split} \mathbf{y} &= \mathbf{D_0}' \ \mathbf{D_1} + \mathbf{D_0}' \ \mathbf{D_2}' \\ \mathbf{V} &= \mathbf{D_0} + \mathbf{D_1} + \mathbf{D_2} + \mathbf{D_3} \end{split}$$

## Problem 5 [16 marks]

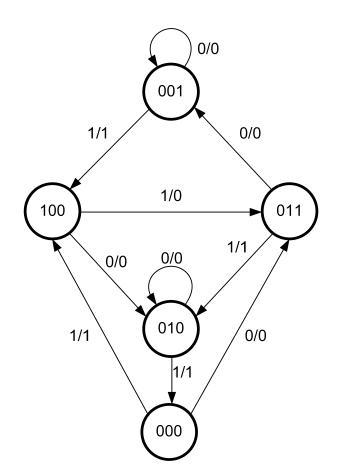

A sequential circuit has three flip-flops, *A*, *B*, *C*; one input *x*, and one output, *y*. The state diagram is shown below. The circuit is designed by treating the unused states as don't care conditions. The final circuit must be analyzed to ensure that it is self-correcting (i.e., if the circuit enters in any of the unused states, after finite number of clock cycles it comes to a used state.). Use *JK* flip-flops for the design.

| I              | Present State | e | Input |                | Next State |   | Output         |

|----------------|---------------|---|-------|----------------|------------|---|----------------|

| Α              | В             | С | x     | А              | В          | С | y              |

| 0              | 0             | 0 | 0     | 0              | 1          | 1 | 0              |

| 0              | 0             | 0 | 1     | 1              | 0          | 0 | 1              |

| 0              | 0             | 1 | 0     | 0              | 0          | 1 | 0              |

| 0              | 0             | 1 | 1     | 1              | 0          | 0 | 1              |

| 0              | 1             | 0 | 0     | 0              | 1          | 0 | 0              |

| 0              | 1             | 0 | 1     | 0              | 0          | 0 | 1              |

| 0              | 1             | 1 | 0     | 0              | 0          | 1 | 0              |

| 0              | 1             | 1 | 1     | 0              | 1          | 0 | 1              |

| 1              | 0             | 0 | 0     | 0              | 1          | 0 | 0              |

| 1              | 0             | 0 | 1     | 0              | 1          | 1 | 0              |

|                |               |   |       |                |            |   |                |

|                |               |   |       | T              |            |   |                |

| J <sub>A</sub> | K             |   | $J_B$ | K <sub>B</sub> |            | С | K <sub>C</sub> |

| 0              |               | K | 1     | Х              |            | 1 | Х              |

| 1              |               | K | 0     | Х              |            | ) | Х              |

| 0              |               | K | 0     | Х              |            | K | 0              |

| 1              |               | K | 0     | Х              | 2          | X | 1              |

| 0              | Σ             | K | Х     | 0              | (          | ) | Х              |

| 0              | Σ             | K | Х     | 1              | (          | ) | Х              |

| 0              |               | K | Х     | 1              |            | X | 0              |

| 0              | Σ             | K | Х     | 0              |            | X | 1              |

| Х              | ]             | l | 1     | Х              | (          | ) | Х              |

| Х              | 1             | 1 | 1     | Х              |            | 1 | Х              |

| $J_A = B'x$ | $J_B = A + C'x'$  | $J_C = Ax + A'B'x'$ |

|-------------|-------------------|---------------------|

| $K_A = 1$   | $K_B = C'x + Cx'$ | $K_C = x$           |

Self-correction because  $K_A = 1$

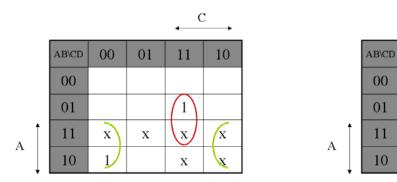

**Problem 6 [14 marks]** Design a synchronous BCD counter with *Data* flip-flops.

|   | Presen | t State |   |   | Next | State |   |

|---|--------|---------|---|---|------|-------|---|

| А | В      | С       | D | А | В    | С     | D |

| 0 | 0      | 0       | 0 | 0 | 0    | 0     | 1 |

| 0 | 0      | 0       | 1 | 0 | 0    | 1     | 0 |

| 0 | 0      | 1       | 0 | 0 | 0    | 1     | 1 |

| 0 | 0      | 1       | 1 | 0 | 1    | 0     | 0 |

| 0 | 1      | 0       | 0 | 0 | 1    | 0     | 1 |

| 0 | 1      | 0       | 1 | 0 | 1    | 1     | 0 |

| 0 | 1      | 1       | 0 | 0 | 1    | 1     | 1 |

| 0 | 1      | 1       | 1 | 1 | 0    | 0     | 0 |

| 1 | 0      | 0       | 0 | 1 | 0    | 0     | 1 |

| 1 | 0      | 0       | 1 | 0 | 0    | 0     | 0 |

$d(A,B,C,D) = \sum (10,11,12,13,14,15)$

$D_A = AD' + BCD$

$\mathbf{D}_{\mathbf{B}}^{=} \mathbf{B}\mathbf{C'}^{+} \mathbf{B}\mathbf{D'}^{+} \mathbf{B'}\mathbf{C}\mathbf{D}$

00

1

x

01

1

X

С

10

1

X

х

+

11

1

х

$\widehat{\mathbf{x}}$

$\mathbf{D}_{\mathbf{C}} = \mathbf{C}\mathbf{D'} + \mathbf{A'C'D}$

C C -00 AB\CD 01 11 10 1 00 1 1 01 1 11 х х х х 1 10 X х

А

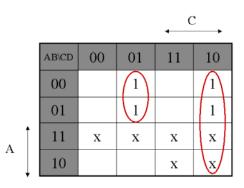

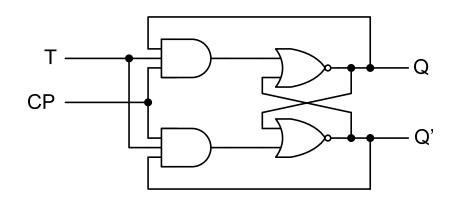

### Problem 7 [10 marks]

Analyze a given toggle flip-flop as shown below as an asynchronous sequential circuit. Obtain the transition table and show that the circuit is unstable when both T and CP are equal to 1.

Let CP = C, Q = YS = TCy' R = TCyY = S + R'y= TCy' + (TCy)' y= TCy' + Ty' + C'yТ y∖TC 00 01 11 10 1 0 0 0 0 1 1 0 у 🕽 1 1

→ when T =1 and C = 1 then  $Y \neq y$  → circuit is unstable.

## Problem 8 [16 marks]

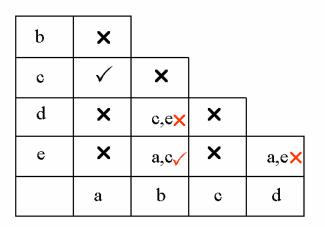

The state table of an asynchronous circuit with three SR latches is shown below. Reduce the number of states in the state table using implication table.

| Present State | Input | Next State | Flip-flop Inputs  | Output |

|---------------|-------|------------|-------------------|--------|

| ABC           | Х     | ABC        | SA RA SB RB SC RC | Y      |

| 001           | 0     | 001        | 0 X 0 X X 0       | 0      |

| 001           | 1     | 010        | 0 X 1 0 0 1       | 0      |

| 010           | 0     | 011        | 0 X X 0 1 0       | 0      |

| 010           | 1     | 100        | 1 0 0 1 0 X       | 1      |

| 011           | 0     | 001        | 0 X 0 1 X 0       | 0      |

| 011           | 1     | 010        | 0 X X 0 0 X       | 0      |

| 100           | 0     | 101        | X 0 0 X 1 0       | 0      |

| 100           | 1     | 100        | X 0 0 X 0 X       | 1      |

| 101           | 0     | 001        | 0 1 0 X X 0       | 0      |

| 101           | 1     | 100        | X 0 0 X 0 1       | 1      |

| State\Input | $\mathbf{x} = 0$ | x = 1 |

|-------------|------------------|-------|

| a (001)     | a,0              | b,0   |

| b (010)     | c,0              | d,1   |

| c (011)     | a,0              | b,0   |

| d (100)     | e,0              | d,1   |

| e (101)     | a,0              | d,1   |

(a,c) , (e,b), (d)