| Typical ga      | Typical gate characteristics (two input NAND) |         |               |                       |  |  |  |  |

|-----------------|-----------------------------------------------|---------|---------------|-----------------------|--|--|--|--|

|                 | Noise<br>Margin<br>(V)                        | Fan-out | Power<br>(mW) | Nominal<br>Delay (ns) |  |  |  |  |

| TTL             | 0.4                                           | 10      | 10            | 10                    |  |  |  |  |

| Schottky<br>TTL | 0.4                                           | 10      | 20            | 3                     |  |  |  |  |

| ECL             | 0.15                                          | 25      | 25            | 0.05                  |  |  |  |  |

| CMOS            | 0.5                                           | 4       | 0.001         | 0.1                   |  |  |  |  |

|                 |                                               |         | (100 Mhz)     |                       |  |  |  |  |

|                             | MSI  | PLDs              | Programmable<br>Gate Arrays | Gate<br>Arrays  | Custom<br>VLSI |  |

|-----------------------------|------|-------------------|-----------------------------|-----------------|----------------|--|

| Integration in<br>Gates     |      |                   | 1k-10M                      | 1k-100k         | 1k-100M        |  |

| Speed                       | Fast | Slow to<br>Medium | Slow to Medium              | Slow to<br>Fast | Fast           |  |

| Function<br>defined by User | No   | Yes               | Yes                         | Yes             | Yes            |  |

| Time to<br>Customize        |      |                   | Seconds                     | Weeks           | Months         |  |

| User<br>Programmable        | No   | Yes               | Yes                         | No              | No             |  |

Department of Electrical Engineering, University of Waterloo

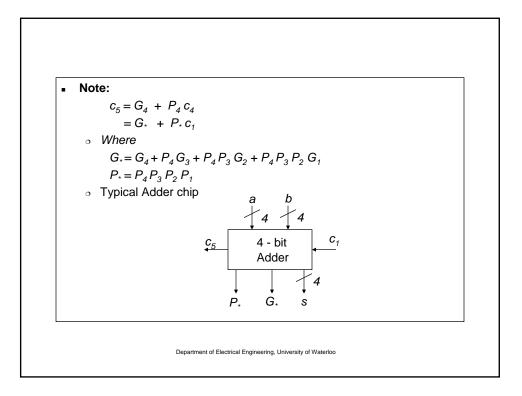

| Observe:                                                                     | ] |

|------------------------------------------------------------------------------|---|

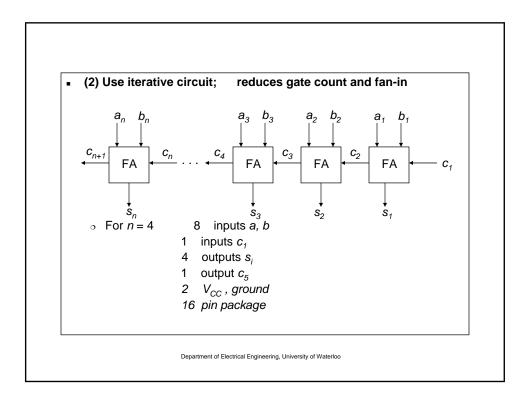

| <ul> <li>All carries can be generated simultaneously</li> </ul>              |   |

| $c_2 = G_1 + P_1 c_1$                                                        |   |

| $c_2 = c_1 + r_1 c_1$<br>$c_3 = G_2 + P_2 c_2 = G_2 + P_2 G_1 + P_2 P_1 c_1$ |   |

| $c_4 = G_3 + P_3 c_3 = G_3 + P_3 G_2 + P_3 P_2 G_1 + P_3 P_2 P_1 c_1$        |   |

| • Delay?                                                                     |   |

| $P_i, G_i$                                                                   |   |

| XOR and AND 2 gate delays                                                    |   |

| $= C_i \longrightarrow$                                                      |   |

| two-level AND - OR 2 gate delays                                             |   |

| $s_i \rightarrow s_i$                                                        |   |

| XOR 2 gate delays                                                            |   |

| 6 gate delays independent of n                                               |   |

| <ul> <li><i>n</i> limited by connections and gate loading</li> </ul>         |   |

|                                                                              | ] |

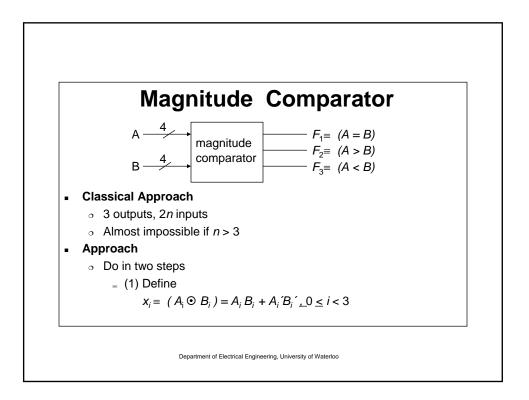

$$\begin{aligned} & = (2) \text{ Now} \\ & F_1 = (A = B) = x_3 x_2 x_1 x_0 \\ & F_2 = (A > B) = (A_3 > B_3) \\ & + (A_3 = B_3) \bullet (A_2 > B_2) \\ & + (A_3 = B_3) \bullet (A_2 = B_2) \bullet (A_1 > B_1) \\ & + (A_3 = B_3) \bullet (A_2 = B_2) \bullet (A_1 = B_1) \bullet (A_0 > B_0) \\ & = A_3 B'_3 + x_3 A_2 B'_2 + x_3 x_2 A_1 B'_1 + x_3 x_2 x_1 A_0 B'_0 \end{aligned}$$

| Pri<br>More than 1 active in | nput         | line            |        |                       |        |        |        |

|------------------------------|--------------|-----------------|--------|-----------------------|--------|--------|--------|

| Output corresponds           |              | -               |        |                       | -      |        | -      |

| -                            | <u></u><br>Х | <u>D</u> 1<br>X | 2<br>X | <i>D</i> <sub>3</sub> | 1      | y<br>1 | z<br>1 |

|                              |              |                 |        |                       | 1      |        |        |

|                              | x            | 1               | 0      | 0                     | 1      | 0      | 1      |

|                              | 1            | 0               | 0      | 0                     | 1<br>0 | 0      | 0      |

|                              | 0            | 0               | 0      | 0                     | 0      | 0      | 0      |

|                              |              |                 |        |                       |        |        |        |

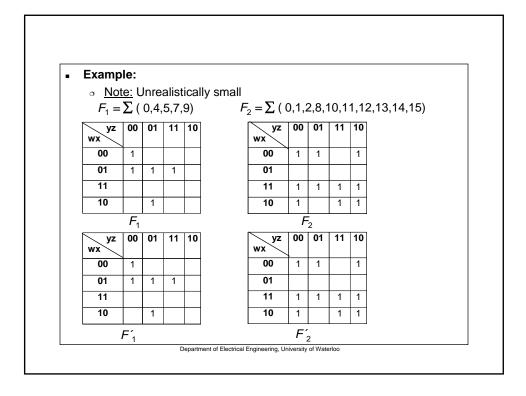

| • $F_1 = W y z + W x z +$                                                                                  |                         |        |        |        | $F_2 = w'x'y' + wx + wy + x'z'$ |            |                       |  |  |

|------------------------------------------------------------------------------------------------------------|-------------------------|--------|--------|--------|---------------------------------|------------|-----------------------|--|--|

| $F'_1 = w'x'z' + yz' + wx$                                                                                 | (+ <i>wz</i> + <i>w</i> | y F    | =´2 =  | ẃx     | + WX                            | í ý ź      |                       |  |  |

| or = w'x'z' + yz' + wx                                                                                     | + wz´+ x´)              | /      |        |        |                                 |            |                       |  |  |

| <ul> <li>Select whichever of</li> </ul>                                                                    |                         |        |        |        |                                 |            |                       |  |  |

| <ul> <li>F<sub>1</sub>F<sub>2</sub>, F<sub>1</sub>F<sub>2</sub>, F<sub>1</sub>', F<sub>1</sub>'</li> </ul> | $F_2$ or $F'_1 F$       | ,<br>2 |        |        |                                 |            |                       |  |  |

| minimizes the nun                                                                                          | nber of pro             | duct   | terms  | 5      |                                 |            |                       |  |  |

| (Number of produc                                                                                          | t terms is t            | he lir | niting | ) fact | or)                             |            |                       |  |  |

| <ul> <li>PLA specification</li> </ul>                                                                      | product                 | inputs |        |        |                                 | outputs    |                       |  |  |

|                                                                                                            | term                    | w      | x      | У      | z                               | <b>F</b> 1 | <b>F</b> <sub>2</sub> |  |  |

| w´y´z´                                                                                                     | 1                       | 0      | -      | 0      | 0                               | 1          | -                     |  |  |

| w´xz                                                                                                       | 2                       | 0      | 1      | -      | 1                               | 1          | -                     |  |  |

| wx´y´z                                                                                                     | 3                       | 1      | 0      | 0      | 1                               | 1          | 1                     |  |  |

| w´x                                                                                                        | 4                       | 0      | 1      | -      | -                               | -          | 1                     |  |  |

| w´yz                                                                                                       | 5                       | 0      | -      | 1      | 1                               | -          | 1                     |  |  |

| ·                                                                                                          | true / c                | omp    | leme   | nt –   | *                               | Т          | С                     |  |  |