# Constant-RMR Implementations of CAS and Other Synchronization Primitives Using Read and Write Operations

Wojciech Golab\* HP Labs, Palo Alto, USA wojciech.golab@hp.com Vassos Hadzilacos\* University of Toronto, Canada vassos@cs.toronto.edu

Danny Hendler

Ben-Gurion University, Israel

hendlerd@cs.bgu.ac.il

Philipp Woelfel\*

University of Calgary, Canada

woelfel@cpsc.ucalgary.ca

May 28, 2011

#### Abstract

We consider asynchronous multiprocessors where processes communicate only by reading or writing shared memory. We show how to implement consensus, compare-and-swap (CAS) and other comparison primitives, as well as load-linked/store-conditional (LL/SC) using only a *constant* number of remote memory references (RMRs), in both the cache-coherent and the distributed-shared-memory models of such multiprocessors. Our implementations are blocking, rather than wait-free: they ensure progress provided all processes that invoke the implemented primitive are live.

Our results imply that *any* algorithm using read and write operations, comparison primitives, and load-linked/store-conditional, can be simulated by an algorithm that uses read and write operations only, with at most a constant-factor increase in RMR complexity.

**Keywords:** Comparison primitives, consensus, load-linked/store-conditional, mutual exclusion, remote memory references, shared memory.

<sup>\*</sup>Supported partially by the Natural Sciences and Engineering Research Council (NSERC) of Canada.

### 1 Introduction

Work on synchronization in shared memory multiprocessors has largely focused on the asynchronous model, either with or without crash failures. In wait-free synchronization, each process must make progress through its own steps regardless of the execution speeds or crash failures of others; in blocking synchronization, processes may busy-wait for others by repeatedly accessing shared memory, and so progress is guaranteed only when every active process is live. (A process is live if, whenever it begins executing an algorithm, it continues to take steps until the algorithm terminates.)

In this paper we focus on blocking synchronization in asynchronous multiprocessors where processes communicate through shared memory. A natural way to measure the time complexity of algorithms in such multiprocessors is to count the number of memory accesses. This measure is problematic for blocking algorithms because, in this case, a process may perform an unbounded number of memory accesses while busy-waiting for another process. (For example, this happens in a mutual exclusion algorithm when a process waits for another to clear the critical section.) Instead, we can measure the time complexity of an algorithm by counting only remote memory references (RMRs), i.e., memory accesses that traverse the processor-to-memory interconnect. Local-spin algorithms, which perform busy-waiting by repeatedly reading shared variables that can be accessed locally, achieve bounded RMR complexity and have practical performance benefits [4].

The classification of memory accesses into local and remote depends on the memory model of the multiprocessor: In the distributed shared memory (DSM) model, a variable's physical address determines locality with respect to a processor, each variable being local to exactly one processor and remote to all others. In the cache-coherent (CC) model, processors operate on cached copies of shared variables, and it is the state of a processor's local cache combined with the action of the coherence protocol (which keeps consistent copies of a variable in different caches) that determines locality. A memory access is local if it results in a cache hit and can be resolved without accessing main memory or a remote cache; a memory access is remote otherwise. To analyze the worst-case RMR complexity of an algorithm, we assume that each process runs on a distinct processor. (For this reason, we speak of processes and processors interchangeably.)

The main theme of this paper is that certain popular synchronization primitives can be implemented efficiently in software, at least in terms of RMRs, from simpler ones. A synchronization primitive, in this context, is a type of operation that acts on a shared state abstractly represented by a memory word. We model an implementation of a set  $\mathcal{S}$  of primitives as a typed shared object that supports an atomic operation on its state corresponding to each primitive in  $\mathcal{S}$ . Such an object supporting only read and write primitives is called a  $read/write\ register$  (or just register).

#### Summary of results.

- (1) All comparison primitives [2], a class of synchronization primitives that includes the popular compare-and-swap (CAS) primitive, can be implemented using read and write operations with only a constant number of RMRs, in both the DSM and CC models. The same holds for the load-linked/store-conditional (LL/SC) pair of primitives. In both cases we show how to make the implementation readable and writable (i.e., we show how to support read and write primitives on the shared object).

- (2) Our constant-RMR implementations can be made *locally-accessible* just like their hard-ware-implemented counterparts. In the DSM model, this means that the implemented object behaves as if it is local to some processor, and so some designated process can access the object without performing any RMRs. (This is nontrivial because the implemented object may use internally many base objects, not all local to the designated process.) Similarly, in the CC model the object behaves as if it can be cached, meaning that certain operations on an "in-cache" object cost

no RMRs; whether an object is "in-cache" depends on the prior history of the execution and the coherence protocol. (This again is nontrivial because the implemented object may use internally many base objects and access them in complex ways.)

(3) As a consequence of (1) and (2), any CC or DSM shared memory algorithm using read, write, comparison primitives and LL/SC can be simulated by an algorithm that uses only read and write operations, with only a constant-factor increase in the RMR complexity, while preserving other important properties.

Our constant-RMR implementations of comparison primitives and LL/SC are obtained in a series of steps. We first show how to transform any leader election algorithm that uses read and write operations into a name consensus algorithm that uses read and write operations and has the same worst-case RMR complexity to within a constant factor. (In a leader election algorithm, exactly one active process declares itself the winner, and all others declare themselves losers. In a name consensus algorithm, all active processes agree on one of their IDs.) Since there is a constant-RMR leader election algorithm [13], this transformation yields a constant-RMR name consensus algorithm. This efficient name consensus algorithm is used, in turn, to obtain constant-RMR CAS and LL/SC implementations from reads and writes. Finally, we observe that using CAS and no additional RMRs, one can easily implement any combination of comparison primitives.

Related work and implications of our results. Herlihy has shown that synchronization primitives vary widely in their ability to support wait-free implementations, and can be classified in the wait-free hierarchy, where the level of a primitive corresponds to its power [16]. For example, CAS together with read and write operations supports wait-free implementations of arbitrary objects shared by any number of processes; as a result, CAS is at the top level of the wait-free hierarchy. In contrast, the primitive fetch-and-store (FAS), together with read and write operations, supports wait-free implementation of arbitrary objects shared by at most two processes; as a result, FAS is at level two of the wait-free hierarchy. (FAS atomically reads a shared memory location and overwrites it with a value that is fixed in advance.)

As regards blocking synchronization, however, all primitives can be implemented using only read and write operations, by using such operations to implement mutual exclusion [9]. Thus, it is not meaningful to compare the power of two primitives by asking whether one can be used, along with read and write operations, to implement the other. Instead of comparing the power of two primitives based on computability, it is natural to ask whether we can base such a comparison on complexity — specifically, the RMR complexity of implementing a given primitive using read and write operations. From this point of view, we define the RMR complexity of a primitive, denoted C, as the minimum of worst-case RMR complexity over all implementations of that primitive using read and write operations; and we say that a primitive S is stronger than a primitive W if and only if C(S) is greater asymptotically than C(W).

Looking at the relative power of primitives from this perspective reveals a landscape very different from that of Herlihy's wait-free hierarchy [16]. Some primitives classified as strong in the wait-free hierarchy have low RMR-cost implementations from read and write operations, and are weak in their ability to solve mutual exclusion efficiently in terms of RMRs. Conversely, some primitives classified as weak in the wait-free hierarchy have inherently high RMR-cost implementations from reads and writes, and yield the most RMR-efficient mutual exclusion algorithms. For example, CAS is at the top of the wait-free hierarchy but, as we show in this paper, it can be implemented from read and write operations using only a constant number of RMRs. On the other hand, FAS is only at level two of the wait-free hierarchy, but any implementation of FAS from read and write operations requires  $\Omega(\log N)$  RMRs in the worst case (where N is a parameter of the implementation that denotes the number of processes that can access it). This follows from the

fact that mutual exclusion can be solved with O(1) RMRs per passage through the critical section using FAS along with read and write operations [6], but requires  $\Omega(\log N)$  RMRs per passage in the worst case using only reads and writes [5]. The same holds for the primitive *fetch-and-add* (FAA) [4], which is also weak in the wait-free hierarchy.

Anderson and Kim were the first to propose a way of ranking synchronization primitives according to their power for solving mutual exclusion efficiently (under the RMR complexity measure) [1], and to contrast this approach with Herlihy's wait-free hierarchy [16]. To that end, they defined for each primitive (and value of N) a numerical rank r that captures in a particular way the primitive's ability to break symmetry among N processes that apply it concurrently to the same variable. They then showed that a primitive of rank  $r \geq 2$  can be used, in conjunction with read and write operations, to solve mutual exclusion using  $O(\max(1, \log_r N))$  RMRs per passage for any N. It is not known whether the latter bound is tight in general, although it is tight for common primitives such as reads and writes, CAS, FAS, and FAA.

Our ranking of synchronization primitives is similar to Anderson and Kim's in that it captures, at least for common primitives, their power to efficiently solve mutual exclusion for any N. The advantage of our ranking scheme over Anderson and Kim's is that it is based on a simpler property of "strength", namely the RMR complexity of implementing a primitive using read and write operations. This property is easier to define than Anderson and Kim's rank. Moreover, the RMR complexity bound obtained to evaluate a primitive's strength, in the sense we propose, is of independent interest.

Our results also have an interesting implication regarding mutual exclusion. To explain this we first recall certain facts about the RMR complexity of mutual exclusion. The most RMR-efficient mutual exclusion algorithm known to date that uses only read and write operations is one devised by Yang and Anderson; it performs  $O(\log N)$  RMRs per passage through the critical section [24]. Attiya, Hendler and Woelfel showed that this is optimal [5], building on a prior  $\Omega(\log N)$  lower bound by Fan and Lynch for a related but different cost model [11]. The optimality result holds for algorithms that use reads and writes only, and tightens a prior  $\Omega(\log N/\log\log N)$  lower bound on RMRs by Anderson and Kim [2] that holds for a broader class of algorithms: those using reads, writes, and comparison primitives. Anderson and Kim posed the question whether  $\Theta(\log N)$  is the tight worst-case RMR complexity lower bound for the latter class of algorithms [2]. We answer this in the affirmative through our result (3), in combination with the  $\Omega(\log N)$  lower bound on RMR complexity of algorithms that use reads and writes only [5]. (For first-come-first-served (FCFS) mutual exclusion, the  $\Omega(\log N)$  lower bound holds a fortiori, but the upper bound of  $O(\log N)$  does not, because the simulation referred to by our result (3) breaks the FCFS property. The tight bound for FCFS mutual exclusion is established in [8].)

#### 1.1 Organization

We describe our model of computation in Section 2. Our implementations of CAS and LL/SC are then derived in Sections 3–8 using a layered approach, which we explain in more detail below. Section 9 then describes how to implement comparison primitives in general, and states our main result (3). In Section 10 we conclude the paper by discussing open problems. To streamline the paper, we defer portions of technical analysis to Appendix A.

Presenting our implementations is challenging as we consider two very different shared memory architectures (CC and DSM) and two shared object types (CAS and LL/SC) that are not easily derived from each other in a manner that preserves correctness properties of interest in this paper. Furthermore, some of the algorithms are quite complex because the implementations are based upon weak base objects (i.e., atomic read/write registers). To simplify matters, we have chosen to

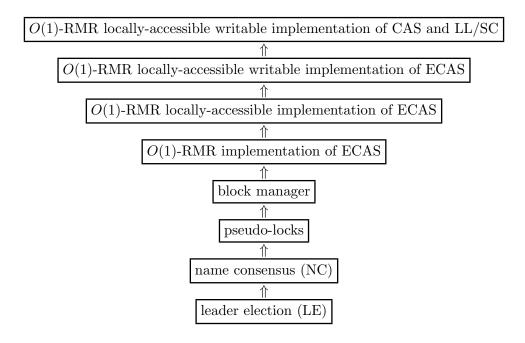

break down the construction into multiple layers, as illustrated in Figure 1.

The starting point in our construction is the leader election (LE) problem where, informally speaking, one of the participating processes is declared as the "winner" and all the others as "losers". A constant-RMR implementation of LE using only reads and writes was presented in [13]. In Section 3, we use LE to solve the Name Consensus (NC) problem where, informally speaking, participating processes agree on the name of the "winner". The constant-RMR reduction of NC to LE using only reads and writes is straightforward in the CC model, but considerably more complex in the DSM model. In Section 4 we use NC to construct a new primitive we call a pseudo-lock, similar to "one-shot" mutual exclusion. Pseudo-locks provide convenient synchronization machinery for dealing with concurrent operations in our other implementations. In Section 5, we use pseudo-locks to implement a block manager—an object similar in spirit to CAS, but specialized for recording pointers to special data structures we call blocks. Blocks can be used to record arbitrary state, such as the value of a CAS object.

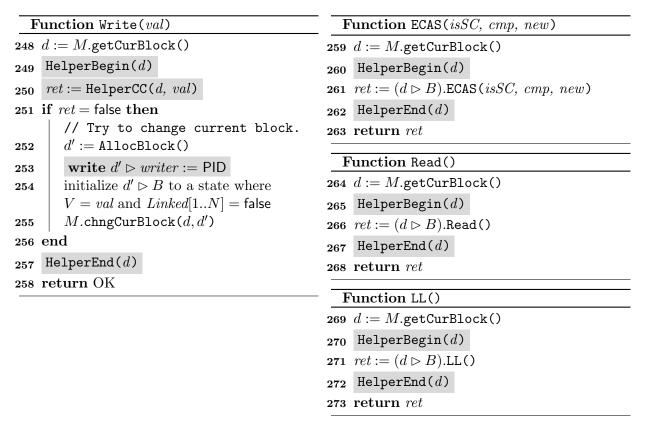

In the layers above the block manager, we present a series of implementations with increasingly powerful properties. In order to address both CAS and LL/SC in a clean way, we introduce a new type called ECAS that generalizes these two primitives. Section 6 defines ECAS and presents a straightforward implementation of ECAS from a block manager. This implementation is sufficient for proving our main result (1) but not our main result (3), which motivates our definition of more powerful locally-accessible implementations in Section 7. Because the latter implementations are defined very differently in the CC and DSM architectures, we are forced from this layer onward to present a separate implementation for each architecture. Next, in Section 8 we show how to make our implementations writable—a feature omitted so far but obtainable easily using techniques developed in earlier sections. Finally, in Section 9 we explain how to instantiate our ECAS implementations to CAS and LL/SC objects that are strong enough to establish our main result (3). Comparison primitive in general are derived trivially from these CAS objects.

Figure 1: Implementation layers.

# 2 Model of Computation and Definitions

Our model of computation is based on Herlihy and Wing's [17].

**Processes and objects.** There are N asynchronous processes. Processes do not fail. The set of processes is denoted  $\mathcal{P} = \{p_1, p_2, ..., p_N\}$ , and we say that  $p_i$  has ID i. Processes communicate by applying operations on shared objects and receiving corresponding responses. Each process repeatedly applies such operations (one at a time) until it terminates, meaning that it has reached a special state where it remains indefinitely and takes no further action. A shared object represents a data structure with a well-defined set of states, as well as a set of operation types. The operation type determines the state transition that occurs when an operation of that type is applied to the shared object in a given state, as well as the response of the operation. It encodes the "signature" of the operation (including any arguments), as well as the ID of the process applying the operation. Processes and objects can be formally modeled as input/output automata [21], but here we adopt a more informal approach by describing the possible behaviours of processes and shared objects through pseudo-code. In pseudo-code, we refer to shared objects as variables.

**Steps.** A process interacts with shared objects by applying operations on these objects. We consider two types of operations: atomic and non-atomic. Atomic operations are instantaneous, and are represented as  $atomic \ steps$ . An atomic step where process p applies an operation of type ot to object v and receives response ret is denoted (p, v, ot, ret). Non-atomic operations are represented using separate invocation and  $response \ steps$ . An invocation step where process p invokes operation type ot on object v is denoted (INV, p, v, ot). A response step where process p receives response p receives response p from an operation execution on object p is denoted (RES, p, v, ret). We say that a response step p matches an invocation step if the two steps are applied by the same process to the same shared object.

**Histories.** A history H is a sequence of steps generated by processes. We explain how histories are generated later on and focus for now only on their building blocks. An operation execution in H is a pair consisting of an invocation step and the next matching response step, or just an invocation step if no matching response follows. We call an operation execution complete in the former case, and pending in the latter. Operation execution ox precedes operation execution ox' in H if the response of ox occurs before the invocation of ox' in H. We say that ox and ox' are concurrent in H if neither precedes the other. A history H is sequential if it only contains atomic steps, or if it only contains complete operation executions no two of which are concurrent. If H is sequential, then |H| denotes the number of atomic steps or operation executions in H.

For any history H and set P of processes, we denote by H|P the subsequence of H consisting of all steps by processes in P. Similarly, for any set V of shared objects, we denote by H|V the subsequence of H consisting of all steps on objects in V. For a process p or object v, we use H|p and H|v as shorthands for  $H|\{p\}$  and  $H|\{v\}$ , respectively. We say that H is a history over V if H = H|V.

For any history H, we say that a process p is *active* in H if H|p is not empty. An infinite history H is fair if every process that is active in H either takes infinitely many steps or terminates.

Object types and conformity to a type. Every shared object has a type  $\tau = (S, s_{init}, \mathcal{O}, \mathcal{R}, \delta)$  where S is a set of states,  $s_{init} \in S$  is the initial state,  $\mathcal{O}$  is a set of operation types,  $\mathcal{R}$  is the set of responses, and  $\delta : S \times \mathcal{O} \to S \times \mathcal{R}$  is a (one-to-many) state transition mapping. The transition

mapping  $\delta$  is intended to capture the behaviour of objects of type  $\tau$ , in the absence of concurrency, as follows: if a process applies an operation of type ot to an object of type  $\tau$  that is in state s, then the object may return to the process a response r and change its state to s' if and only if  $(s',r) \in \delta(s,ot)$ . An object v conforms to type  $\tau$  in a sequential history H if the steps in H|v are consistent with some sequence of transitions of  $\delta$  starting from state  $s_{init}$ , in the following sense: Letting  $ot_i$  and  $ret_i$  denote the operation type and response of the i'th atomic step or operation execution in H|v, and letting k = |H|v|, there exists a sequence  $\langle s_0, s_1, s_2, ..., s_k \rangle$  of states (in  $\mathcal{S}$ ) such that  $s_0 = s_{init}$ , and  $(s_i, ret_i) \in \delta(s_{i-1}, ot_i)$  holds for all  $i \leq k$ .

**States.** Let H be a sequential history over some set  $\mathcal{B}$  of objects, such that every object  $v \in \mathcal{B}$  conforms to its type in H. For any  $k \leq |H|$ , the *state of the system* (or simply "the state") after k atomic steps or operation executions in H is denoted H[k], and consists of the following: the state of each shared object and the *private state* of each process. The private state of a process comprises the values of private variables, in particular a "program counter" that determines the next pseudo-code statement executed by that process (and whether the process has terminated).

Concurrent systems. A concurrent system models algorithms where processes apply atomic steps on a set of shared objects. Formally, it is a tuple  $S = (\mathcal{P}, \mathcal{B}, \mathcal{H})$  where  $\mathcal{P}$  is the set of processes,  $\mathcal{B}$  is the set of shared objects, and  $\mathcal{H}$  is the set of histories of the concurrent system. We will define  $\mathcal{H}$  informally through pseudo-code, consisting of one or more functions for each process, which are typically called according to some specific rules (e.g., each function is called at most once). The set  $\mathcal{H}$  then consists of histories generated by recording an atomic step for each access to a shared object incurred by processes as they execute their functions.

Implementations of shared objects. An implementation describes how to simulate a target object of a particular target type using a set of base objects of specified types. It is formally denoted as a tuple  $I = (\tau, \mathcal{P}, \mathcal{B}, \mathcal{H})$  where  $\tau$  is the target object type,  $\mathcal{P}$  is the set of processes,  $\mathcal{B}$  is the set of base objects, and  $\mathcal{H}$  is the set of histories. The histories in  $\mathcal{H}$  are over the base objects in  $\mathcal{B}$  and the target object of type  $\tau$ , denoted  $O_{\tau}$ . Informally, we describe an implementation using pseudo-code to define an access procedure for each operation type ot of the target type and each process p. The pseudo-code for this access procedure describes how process p applies an operation of type ot to the target object, and computes the response of that operation, by applying operations on the base objects. The set  $\mathcal{H}$  consists of histories generated by recording an invocation or response step on the target object whenever a process begins or finishes executing an access procedure (respectively), and an atomic step for each access to a base object in  $\mathcal{B}$ .

Two correctness properties are required in every implementation: linearizability (safety) and termination (liveness).

### Linearizability and termination.

Linearizability [17] is widely accepted as a correctness condition for histories of shared object implementations. Informally, it states that each operation execution on the target object appears to take effect instantaneously at some point between the operation execution's invocation and response (or possibly not at all if the operation execution is pending). Formally, we first define for any history H of an implementation  $I = (\tau, \mathcal{P}, \mathcal{B}, \mathcal{H})$  a completion, which is a history H' of invocation and response steps on the target object  $O_{\tau}$  such that for every process p,  $H'|O_{\tau}|p$  contains the same steps as  $H|O_{\tau}|p$ , except that for any operation execution Op that is pending in H, either Op is discarded from H' or a matching response step follows the invocation step of Op

Figure 2: Shared memory architectures: DSM (left) and CC (right).

in H'. A history H of an implementation  $I = (\tau, \mathcal{P}, \mathcal{B}, \mathcal{H})$  is linearizable with respect to type  $\tau$  if there exists a history  $\bar{H}$  that satisfies the following properties:

- (a) H is a sequential completion of H.

- (b) The total order of operation executions in  $\bar{H}$  is consistent with the partial order of the corresponding operation executions in H.

- (c) The target object  $O_{\tau}$  conforms to type  $\tau$  in  $\bar{H}$ .

The termination property for a shared object implementation  $I = (\tau, \mathcal{P}, \mathcal{B}, \mathcal{H})$  states that for any history H of I, if H is fair then every operation execution on the target object  $O_{\tau}$  in H is complete.

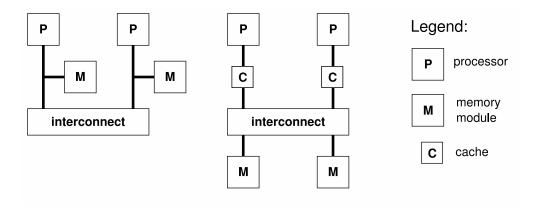

**Local and Remote Memory References.** In this paper, we consider the cache-coherent (CC) and distributed shared memory (DSM) multiprocessor architectures, which are illustrated in Figure 2.

In each architecture, each memory access is either *local* or *remote*, as discussed briefly in Section 1. We now describe these concepts in detail in the context of accesses to the most fundamental of all shared objects: atomic read/write registers. In the DSM model, locality is defined statically: each object is local to exactly one process and is remote to all others, and so counting RMRs is straightforward. In the CC model, however, whether an access to an object is local or remote depends on the type of coherence protocol, and the prior accesses to that object in the history under consideration. We consider two families of cache coherence protocols in this paper: *write-through* and *write-back* [23].

In a write-through protocol, to read an object v a process p must have a (valid) cached copy of v. If it does, p reads that copy without causing an RMR; otherwise, p causes an RMR that creates a cached copy of v. To write v, p causes an RMR that invalidates (i.e., effectively deletes) all other cached copies of v, and writes v to memory (in the same RMR). (The write-through protocol comes in two flavours: with cache invalidation and with cache update upon write. In this paper we consider only the invalidation version, as it is far more common in practice.)

In a write-back protocol, each cached copy is held in either "shared" or "exclusive" mode. To read an object v, a process p must hold a cached copy of v in either mode. If it does, p reads that copy without causing an RMR. Otherwise, p causes an RMR that: (a) eliminates any copy of v held in exclusive mode, typically by downgrading the status of such a copy to shared and, if the exclusive copy was modified, writing that copy to memory; and (b) creates a local cached copy of v held in shared mode. To write v, p must have a cached copy of v held in exclusive mode. If it

does, p writes that copy without causing RMRs. Otherwise, p causes an RMR that: (a) invalidates all other cached copies of v and writes any modified copy held in exclusive mode back to memory; and (b) creates a cached copy of v held in exclusive mode.

In both protocols, a read of object v by process p causes an RMR if and only if p has no (valid) cached copy of v. The protocols differ in the RMRs caused by writes: in write-through, every write causes an RMR; in write-back, a write of v by p causes an RMR if and only if p does not hold a local cached copy of v in exclusive mode.

It is possible to define RMRs precisely in the CC model under certain assumptions that capture "ideal" cache behaviour (e.g., ignoring RMRs due to finite cache size and false sharing). For our purposes, however, it suffices to define simple rules by which we can bound from above the number of RMRs incurred in a history. (We state these for sequential histories over atomic read/write registers here, and then generalize to other types of shared objects in Section 7.) For any history H of atomic steps over a read/write register object v, and for any process p, each atomic step by p causes an RMR, except in the situations described below.

In the write-through CC model:

(R) If H' is a contiguous subsequence of H where each atomic step is a read, then p's atomic steps in H' cause at most one RMR in total (to load v into p's cache).

In the write-back CC model, condition (R) holds, and furthermore:

(W) If H' is a contiguous subsequence of H where each atomic step is applied by p, then the atomic steps in H' cause at most two RMRs in total (to load v into p's cache, and then possibly to promote p's local copy of v from shared to exclusive.)

**Notation.** We use the following notational conventions. In pseudo-code,  $p_i$  denotes the process ID i, and PID denotes the ID of the executing process. We denote by  $\mathbf{read}(var)$  a read of shared variable var, returning the value read. Similarly, we denote by  $\mathbf{write}\ var := val$  a write of val to shared variable var. We denote by  $\mathbf{await}\ cond$  a busy-wait loop that repeatedly evaluates condition cond, and terminates when cond evaluates to true. The symbol  $\triangleright$  in pseudo-code denotes access to a data structure field through a pointer, and is analogous to the operator  $\rightarrow$  in C++ (e.g.,  $d \triangleright f$  denotes a field f in a data structure pointed to by d). We use a variety of typefaces in pseudo-code to distinguish various programming constructs:  $\mathbf{reserved}\ \mathbf{keyword}$ , variable, FunctionName and  $\mathbf{constantName}$ . Comments are formatted in C++ style. Since we use pseudo-code to define both the transition mappping of a shared object type and a specific implementation of the type, we distinguish between the two by enclosing transition mapppings in a  $\mathbf{box}$ .

### 3 Consensus

In this section, we obtain an O(1)-RMR consensus algorithm for N processes using reads and writes only. We consider the special case of consensus known as name consensus, from which ordinary consensus follows by a straightforward transformation that preserves RMR complexity, with only O(1) additional RMRs per process.

Roughly speaking, in the name consensus (NC) problem the active processes must all agree on a common value, which is the name (ID) of one of them. A process wins if its name is agreed upon and loses otherwise. The problem is formally defined as follows. First, since NC is a "one-shot" problem, processes must satisfy the following:

Condition 3.1. Each process calls NameDecide() at most once.

The correctness properties of name consensus are then defined as follows:

**Specification 3.2** (safety). For any history where Condition 3.1 holds:

- (a) Each call to NameDecide() that terminates returns the ID of a process that has made a call to NameDecide().

- (b) No two calls to NameDecide() return different values.

**Specification 3.3** (liveness). For any fair history where Condition 3.1 holds, each call to NameDecide() terminates.

Name consensus is nontrivial in our model because the winner must be an active process, and not every process is required to be active; this rules out the naive algorithm that simply returns the ID of some fixed process.

We distinguish name consensus from the leader election (LE) problem, which was solved with O(1) RMRs using reads and writes in [13]. In the leader election problem, each active process executes a function LeaderElect(), which returns win to exactly one process (the leader or winner), and lose to all others. More formally, leader election is specified as follows:

Condition 3.4. Each process calls LeaderElect() at most once.

**Specification 3.5** (safety). For any history where Condition 3.4 holds:

- (a) If a call to LeaderElect() terminates, then it returns either win or lose.

- (b) At most one call to LeaderElect() returns win.

- (c) If each call made to LeaderElect() terminates, then exactly one such call returns win.

**Specification 3.6** (liveness). For any fair history where Condition 3.4 holds, each call to LeaderElect() terminates.

Leader election is trivial to solve using name consensus (by comparing the winner's ID to the caller's ID). Similarly, in the CC model name consensus is easy to solve using leader election with only O(1) additional RMRs per process. An algorithm that does this is presented in Figure 3. In this algorithm, processes first execute a leader election algorithm L (line 1) and then either read or write a shared variable leader initialized to  $\bot$ . The winner of L writes its ID to leader (line 2) and returns its own ID; other processes wait for leader  $\ne \bot$  (line 4) and then return the value written to leader by the winner. We will refer to the corresponding concurrent system (see Section 2) as  $\mathcal{A}_{NC\text{-}CC}$ . It is straightforward to show that  $\mathcal{A}_{NC\text{-}CC}$  satisfies Specifications 3.2 and 3.3, and that NameDecide() incurs only one more RMR than L in the CC model. Thus, if we instantiate L with

a LE algorithm that uses only reads/writes and O(1) RMRs per process in the CC model, such as the algorithm given in [13], we obtain a NC algorithm that uses only reads/writes and O(1) RMRs per process in the CC model.

####

Figure 3: Name consensus algorithm for the CC model.

In the DSM model, the above algorithm is correct but has poor worst-case RMR complexity. This is because the variable leader is local to exactly one process, and for all others the busy-wait loop at line 4 may generate an unbounded number of RMRs. (At line 4 a process reads leader repeatedly until leader  $\neq \bot$  holds, which may require an unbounded number of reads due to asynchrony.) In modifying this algorithm to achieve bounded RMR complexity in the DSM model, we must allow each process that does not win L to busy-wait on its own locally-accessible shared variable until the winner is chosen. The winner must ensure that all of these variables are written, but it cannot write them itself using only O(1) RMRs because there may be up to N-1 such variables, all remote to the winner. The technique presented in [13] for sharing work does not solve this problem because the winner does not know the IDs of all the processes that may be waiting for it (and hence are capable of sharing work). Nevertheless, a name consensus algorithm that builds on leader election is quite natural, and, as we show in the remainder of this section, is possible to construct with O(1)-RMR overhead in the DSM model using read and write operations. For the remainder of this section, we focus on the DSM model.

### 3.1 Name Consensus in the DSM Model: A High-Level Description

We now show how to solve name consensus at a cost of O(1) RMRs per process in the worst case in the DSM model. Our implementation uses as a building block an O(1)-RMR leader election algorithm L that uses only read/write registers, such as the one presented in [13], as well as some additional read/write registers. Our approach can also be used to construct a name consensus algorithm using any leader election algorithm, with at most a constant-factor increase in worst-case RMR complexity.

The way we use L is derived from the following simple observation: After any history of a leader election algorithm in which all active processes terminate, there is a "data flow" from the process elected leader to any other active process. We can define the notion of data flow more precisely using graph-theoretic concepts. For each process p, we first define the following sets in the context of p's execution of L:

- $W_p$  set of processes to which the variables written remotely by p are local

- $R_p$  set of processes that wrote the values p read remotely (N.B.:  $R_p$  is not necessarily the set of processes to which the variables read remotely by p are local. For example, if process p reads a remote variable p that is local to process p, and the value that p reads in p was written by process p, then p records p and not p.

Next, let G = (V, E) be the directed graph where V is the set of processes, and  $(p, q) \in E$  if and only if  $q \in W_p$  (i.e., p wrote remotely to q's memory) or  $p \in R_q$  (i.e., q read remotely a value written by p). If l is the process elected leader in L, then a data flow from l to another process p is a path from l to p in G. We will prove later (see Lemma 3.14) that there is such a path from l to every active process. Intuitively, this is because if such a data flow does not exist, we can construct a new execution of algorithm L in which only processes to which such paths do not exist are active, and they behave exactly as in the execution of L that gave rise to G; these processes would elect l, which is not active in this new execution.

The high-level idea behind the NC algorithm is as follows. The leader l elected in L writes its ID in a variable leader, and will be the winner agreed on in NC. It then signals its out-neighbours in G to let them know that the winner's name has been decided; once signalled, each neighbour repeats this step: it signals its out-neighbours; and so on. By our earlier observation, that there is a path from l to all active processes in G, eventually all active processes will in fact be signalled, and each can simply read the winner's name from leader.

A number of issues must be addressed for this idea to work, and moreover to work with the required O(1)-RMR complexity per process:

- (a) A process p does not always know all its out-neighbours: it knows the out-neighbours in  $W_p$ , but does not necessarily know every q such that  $p \in R_q$ .

- (b) In fact, because of asynchrony, p might not be able to *ever* discover some of its out-neighbours. For example, suppose that p executes the NC algorithm (and within it L) and writes some register. After p terminates, q "wakes up" and reads a value written by p while executing L, so that  $p \in R_q$ . Thus, q is an out-neighbour of p, and yet p has finished the NC algorithm and cannot be expected to signal q.

- (c) Even if a process p knows all its out-neighbours, it cannot signal them by simply writing into their local memory (while they busy-wait) because there may be many processes q such that  $p \in R_q$ . For example, suppose that in the LE portion of the NC algorithm, p writes a value that is read by all other processes. Then p has N-1 out-neighbours, and so if p had to write a variable local to each, it would be using  $\Theta(N)$  RMRs instead of O(1).

We address these issues as follows. To solve (a) and (b), we use an idea introduced in [13]: a "handshaking protocol" that allows a process p to synchronize with each out-neighbour q such that  $p \in R_q$  by either discovering q's ID, or letting q know (in case q becomes active much later than p) that p is "out of the picture". In the former case, q waits for a signal from p. In the latter case, q knows not to wait for p, and can read the winner's ID from some shared variable (e.g., one written by l before p executes its side of the handshaking protocol). Thus, p need not know all of its out-neighbours (which solves (a)), and "latecomers" can discover the winner's ID easily (which solves (b)). Finally, for problem (c) we use a work sharing mechanism from [13] that spreads RMRs among the processes being signalled, namely the out-neighbours of p.

We now describe the building blocks of the name consensus algorithm in detail in Sections 3.2–3.4, and then present the NC algorithm itself in Section 3.5.

### 3.2 Instrumented Leader Election Algorithm

In order to compute the sets R and W defined earlier, processes execute an "instrumented" version of L (denoted  $\hat{L}$ ) rather than using L directly. This algorithm returns the same response as L, and also computes  $R_p$  and  $W_p$  for every active process p. More precisely, we construct  $\hat{L}$  from L as follows: For every register r initialized to value x by L, initialize r to  $(\perp, x)$ . For every uninitialized register r that may be accessed in L, initialize r to  $(\perp, \tilde{x})$  for some arbitrary value  $\tilde{x}$ . Each active

process  $p \in \mathcal{P}$  records  $R_p, W_p \subseteq \mathcal{P}$  as private variables, both initialized to the empty set. To execute  $\hat{L}$ .LeaderElect(), a process p begins by simulating its operations in L.LeaderElect(). If its next operation in L.LeaderElect() writes value x to register r that is local to q, then p writes (p, x) to r, and adds q to  $W_p$  if  $q \neq p$ . Process p also simulates the change in private state following its write of r. If its next operation in L.LeaderElect() reads register r that is local to process q, then p reads r. If (z, x) is the pair that p read, then p adds p to p if p

They key properties of  $\hat{L}$  are captured in the following lemma. Let  $\mathcal{A}_{LE-I-DSM}$  denote the corresponding concurrent system.

### **Lemma 3.7.** For any history H of $A_{LE-I-DSM}$ where Condition 3.4 holds:

- (a) Specifications 3.5 and 3.6 hold.

- (b) Each call to  $\tilde{L}$ .LeaderElect() incurs O(1) RMRs in the DSM model.

- (c) For each process p, the sets  $R_p$  and  $W_p$  generated during a call to  $\hat{L}$ .LeaderElect() have size O(1).

Proof. Let L denote the O(1)-RMR leader election algorithm used to construct  $\hat{L}$ , and note that by our construction of  $\hat{L}$ , Condition 3.4 holds with respect to  $\hat{L}$  in H. Furthermore, each process either receives the same response from  $\hat{L}$ -LeaderElect() as from L-LeaderElect() in H, or it does not complete its call to  $\hat{L}$ -LeaderElect(). Thus, if H violates Specification 3.5 with respect to  $\hat{L}$ , then it does the same with respect to L. Similarly, if H is fair and violates Specification 3.6 with respect to  $\hat{L}$ , then there must be a non-terminating call to L-LeaderElect() in H, and so H violates Specification 3.6 with respect to L. Since L satisfies Specifications 3.5 and 3.6, this implies  $\hat{L}$  does also, and so (a) holds.

For parts (b)–(c), recall that L.LeaderElect() simulates steps of L.LeaderElect(), performing an RMR at each step only if L.LeaderElect() does so, and adding an element to either R or W only when an RMR occurs. Since R and W are private variables, part (b) follows from the O(1) RMR complexity of L. Similarly, for any process p since  $R_p$  and  $W_p$  are initially empty,  $|R_p| + |W_p|$  is bounded from above by the RMR complexity of L, which implies part (c).

### 3.3 Handshaking Protocol

Our handshaking protocol is used by a process p to synchronize with each out-neighbour q such that  $p \in R_q$ . The protocol is similar in spirit to the one presented in [13], but somewhat simpler. For handshaking between p and an out-neighbour  $q \neq p$ , the protocol relies on a two-process O(1)-RMR leader election algorithm for p and q. Such an algorithm must be accessed according to the following etiquette (in addition to Condition 3.4):

Condition 3.8. A two-process algorithm for processes p and q can only be accessed by p and q.

The particular LE algorithm we use is *local to p* meaning that, in addition to Specifications 3.5 and 3.6, it satisfies the following:

**Specification 3.9.** A call to LeaderElect() by process p incurs zero RMRs.

An O(1)-RMR two-process LE algorithm satisfying this property is presented in detail in [13]. We omit the details for lack of space.

The LE algorithm is used for handshaking between p and q as follows: Process p initiates an instance of the algorithm local to itself with each process  $q \neq p$ . Note that by Specification 3.9, p incurs no RMRs in any of these. With respect to any particular process  $q \neq p$ , there are two outcomes of the LE algorithm for p and q: If process q wins, then we say that q contacted p, otherwise q failed to contact p. (This is similar to terminology used in [13].) In the former case (q wins), p eventually loses, and knows that q is an active out-neighbour of p such that  $p \in R_q$ . Thus, q can wait for a signal from p, and p knows that it must signal q. In the latter case (q loses), p eventually wins, and behaves as if q were not active. Thus, p does not signal q, and hence q does not wait for a signal from p.

Note that up to N-1 processes may contact p, and that p incurs zero RMRs handshaking with these processes, since the LE algorithm used is local to p. Also, note that p may contact q even if q failed to contact p, since there may be two "sessions" of the handshaking protocol between p and q, running in "opposite directions."

### 3.4 Signalling Mechanism

As mentioned before, our name consensus algorithm disseminates the leader's ID across the data flow graph G. The straightforward algorithm for doing this, whereby each process p signals all its out-neighbours in G (that it is aware of) by writing into their local memory, is too expensive in terms of RMRs. Instead, we use a signalling mechanism that shares the workload among p's neighbours.

Informally, the signalling mechanism works as follows. When p needs to communicate the leader's ID to a subset  $\mathcal{N}_p$  of its neighbours (e.g., those which p has contacted), it builds a chain of the IDs from  $\mathcal{N}_p$  in its local memory. Process p then signals the first process in the chain, say q, by writing p's ID in a designated location in q's memory. This costs p a single RMR. Each process q that is signalled in this way then reads the leader's ID from p's memory and signals the next process in the chain (if any), whose ID it also reads from p's local memory. The handshaking protocols executed prior to this ensure that for each such process p, all the processes in  $\mathcal{N}_p$  wait for p's (either direct or indirect) signal, as otherwise the signalling mechanism breaks.

The signalling mechanism consists of subroutines signal, wait, and wait-any, which are presented in Figure 4. Function signal(P) tells the processes in set P that some event, for which they are waiting, has occurred. Function wait(q) blocks until a signal by process q occurs. Function wait-any blocks until a signal by any process occurs.

Function signal(P) is implemented as follows. At lines 8–12, the calling process p uses its local Work array to create a "chain" of identifiers from P (all elements of Work[p][1..N] are initially  $\bot$ ). This chain determines the order in which the processes in P signal each other. To bootstrap the signalling mechanism, p assigns true to D[q][p] where q is the process at the beginning of the chain (line 13).

Function wait(q) is the counterpart of signal(P). The argument of wait(q) is the ID of a process q that may signal the caller. The process p executing wait waits for a signal from q by locally spinning on D[p][q] (which is initially false) until a process that precedes it in a signalling chain writes true to D[p][q] (see line 14). At line 15, p reads the identifier of the next process in the chain (if any). If such a process exists, then p signals it (lines 16–18).

We also define a function wait-any, which takes no argument, and terminates when the calling process has been signalled through *any* signalling chain. In contrast to wait, this function does not signal the next process in the chain; a process must call wait subsequently for this to happen. The correctness properties of signal, wait and wait-any, are formally stated by the following lemma.

```

Shared variables:

Work[1..N][1..N] – array of process ID or \bot, initially all \bot, elements Work[p][1..N] local to

process p

D[1..N][1..N] – array of Boolean, initially all false, elements D[p][1..N] local to p

Private variables: (per-process)

prev, next, t – process ID or \bot, uninitialized

Function signal(P)

Input: P \subseteq \mathcal{P}

7 if P = \emptyset then return

// Create a "signalling chain" from elements of P.

8 prev := \bot

9 foreach next \in P do

// Order of chain elements is reverse of loop order.

write Work[PID][next] := prev

10

prev := next

11

12 end

// Signal the first process in the chain.

13 write D[next][PID] := true

Function wait(q)

Function wait-any()

Input: q \in \mathcal{P}

19 loop forever

14 await D[PID][q] = true

// Wait for signal from any

// Identify next process in the

process.

signalling chain.

20

foreach t \in \mathcal{P} do

15 next := read(Work[q][PID])

if D[PID][t] = \text{true then}

21

16 if next \neq \bot then

return

\mathbf{22}

// Signal the next process.

end

23

write D[next][q] := true

17

end

\mathbf{24}

18 end

25 end

```

Declarations for signal, wait and wait-any.

Figure 4: Work-sharing signalling mechanism.

### **Lemma 3.10** (safety). For any history:

- (a) In the DSM model, each call to signal and wait incurs O(1) RMRs, and each call to wait-any incurs zero RMRs.

- (b) Each call to signal performs a bounded number of steps.

- (c) If process p completes a call to wait(q) then q previously made a call to signal(P) with  $p \in P$ .

- (d) If process p completes a call to wait-any() then some process q previously made a call to signal(P) with  $p \in P$ .

### Proof.

Parts (a) and (b): These follow directly from the algorithms and the locality of Work[p][1..N] to process p.

Part (c): Suppose that p completes a call to wait(q). Then p reads D[p][q] = true at line 14. Since this variable is initially false, some process r must have assigned D[p][q] = true, either at line 13 of signal, or at line 17 of wait. In the former case, it follows from the algorithm for signal(P) that r = q and that  $p \in P$ . In the latter case, r read q's ID from Work[q][r] at line 15, which must have been written at line 10 of signal(P), namely by q with  $p \in P$ .

**Part** (d): The proof is a simplified version of the proof of part (c).  $\Box$

### **Lemma 3.11** (liveness). For any fair history:

- (a) If some process q writes true to D[p][q] at line 13 or at line 17, and if p calls wait(q), then p's call terminates.

- (b) If some process q writes true to D[p][q] at line 13 or at line 17, and if p calls wait-any, then p's call terminates.

*Proof.* Part (a): Follows directly from the fact that once a process assigns D[p][q] = true, this variable is never reset back to false. Thus, any call to wait(q) by p in a fair history eventually progresses beyond line 14 and terminates.

Part (b): The proof is analogous to the proof of part (a).

**Lemma 3.12** (liveness). Consider any fair history H where processes call the subroutines signal, wait and wait-any. Consider a particular call to signal (P) in H, say by some process q. Suppose that no other call by q to signal (P') occurs with  $P \cap P' \neq \emptyset$ . Also suppose that in H every process  $p \in P$  either makes a call to wait (q) or makes a non-terminating call to wait-any. Then all the calls to wait (q) and wait-any made in H by processes in P terminate.

Proof. If |P| = 0 then the result follows trivially, so consider the case when  $|P| \ge 1$ . Let  $\sigma = \langle p_1, p_2, ..., p_m \rangle$  be the sequence of process IDs selected at line **9** during q's execution of signal (P) under consideration, in reverse order (i.e., q assigns  $D[p_1][q] = \text{true}$  at line **13**). Note that  $\sigma$  is a sequence over all the elements of P without repetition. Let S(k) represent the following claim: all calls to wait-any and wait under consideration made by the first k processes in  $\sigma$  terminate. We will show that S(k) holds for all  $k \in [1..m]$  by induction on k, which implies the lemma.

**Basis:** S(1) follows from Lemma 3.11 (a) and (b) since q assigns  $D[p_1][q] = \text{true}$  at line 13 during its call to signal (P).

**Induction step:** Suppose that  $m \ge 2$  (i.e.,  $|P| \ge 2$ ). For any  $k \in [2..m]$ , and for all  $i \in [0..k-1]$ , suppose that S(i) holds. We must show that S(k) holds. By the induction hypothesis, it suffices to show that the calls to wait-any and wait(q) by  $p_k$  terminate. To that end, we will show that  $p_k$  assigns  $D[p_k][q] = \text{true}$  at line 17 of wait(q). To see this, first note that by the induction

hypothesis and our assumption on when processes call wait(q),  $p_{k-1}$  eventually calls wait(q) and reads Work[q][PID] at line 15. Since we assume q does not call signal(P') with  $P \cap P' \neq \emptyset$ , it follows that  $p_{k-1}$  reads  $p_k$ 's ID from Work[q][PID], and then assigns  $D[p_k][q] = \text{true}$  at line 17. Consequently, any call to wait-any by  $p_k$  terminates by Lemma 3.11 (b) and any call to wait(q) by  $p_k$  terminates by Lemma 3.11 (a), as wanted.

### 3.5 Name Consensus in the DSM Model: A Detailed Description

The name consensus algorithm (NameDecide()) that uses the instrumented leader election algorithm  $\hat{L}$ , handshaking protocol, and signalling mechanism described earlier, is presented in Figure 5. We will refer to the corresponding concurrent system (see Section 2) as  $\mathcal{A}_{NC-DSM}$ . The algorithm uses  $N^2$  "instances" of a two-process leader election algorithm for handshaking, each instance having its own distinct copy of the underlying shared variables. We denote the instance for p and q, which is local to p, by L2P[p][q].

Leader election using  $\hat{L}$  occurs at line **26**. For each process p, the computation of the sets  $R_p$  and  $W_p$  is performed implicitly by  $\hat{L}$ . We refer to p and q as neighbours if and only if p and q are adjacent (ignoring direction of edges) in the (directed) "data flow" graph G defined in Section 3.1 (i.e.,  $p \in R_q \cup W_q$  or  $q \in R_p \cup W_p$ ). As we prove later, the graph G has useful connectedness properties.

After computing  $R_p$  and  $W_p$ , process p needs to communicate with its neighbours regarding the leader's ID, which is the response (i.e., winner) of the name consensus algorithm. As explained in Section 3.1, the high-level idea is to propagate this response through G, along the directed edges and away from the leader. We refer to this informally as propagating information "downstream" in G, even though G may contain cycles. The leader's ID is itself stored in a global shared register leader, initially  $\perp$ . If p is not the leader, then it attempts to discover the leader's ID using two mechanisms. First, it attempts to "pull" information from an upstream neighbour on a directed path from the leader to p. To that end, p engages in the handshaking protocol described in Section 3.3 and tries to contact every neighbour in  $R_p$ . If p fails to contact some such neighbour then that neighbour already knows the leader's ID and so p can read this ID immediately from leader. On the other hand, if p succeeds in contacting each neighbour then none of these neighbours knows the leader's ID and so p waits for some neighbour (not necessarily one it has contacted) to "push" information to it. More precisely, "push" means that some neighbour signals p and then preads leader. Finally, once p discovers the leader's ID (through either the pull or push mechanism), it pushes information to all its neighbours in  $W_p$ , and to any neighbour that contacted p using the handshaking protocol. For subtle reasons related to the work-sharing signalling mechanism, p may have to perform additional work at this point to ensure that processes it contacted earlier make progress.

Now consider the outcome of executing line **26**. If p is elected leader, then it writes its ID to leader at line **27**. At lines **29–33**, p tries to contact its neighbours from  $R_p$ . (Since  $R_p$  has O(1) elements (see Lemma 3.7 (c)), this takes O(1) RMRs in total.) Here p stores in the set U the IDs of neighbours that were actually contacted. If there is some  $q \in R_p$  that p fails to contact, then q has progressed to line **41**, and so as we show in Lemma 3.15, leader  $\neq \bot$ . If p does not win at line **26** and it contacts each  $q \in R_p$ , then p still does not know the leader when it reaches line **34**. In this case, p waits at line **35** for a signal from any neighbour by calling wait-any().

By the time p reaches line 37,  $leader \neq \bot$  holds, as we show later in Lemma 3.15. Now p must signal some of its neighbours of this. The algorithm deals first with p's downstream neighbours in  $W_p$ . To that end, p calls  $signal(\{q\})$  for each  $q \in W_p$  at line 38. Next, p attempts to communicate with other neighbours downstream of it in G, namely any process q for which  $p \in R_q$  holds, which

```

Declarations

Shared variables: (global)

\hat{L} – instrumented O(1)-RMR leader election algorithm (see Section 3.2)

leader – process ID or \perp, initially \perp

L2P[1..N][1..N] – array of O(1)-RMR two-process LE algorithms, where L2P[p][q] is for p

and q, and is local to p

Private variables: (per-process)

R, W, U, X – sets of process IDs, initially \emptyset

q – process ID, uninitialized

Function NameDecide()

Output: PID of leader

// Execute ''instrumented'' leader election algorithm.

26 if \hat{L}.LeaderElect() = win then

27 | write leader := PID

28 end

// Note: sets R and W have been computed (implicitly) at line 27.

// Try to contact neighbours in R.

29 foreach q \in R do

if L2P[q][PID].LeaderElect() = win then

30

U := U \cup \{q\}

31

end

32

33 end

// If needed, wait for a signal (that leader \neq \bot).

34 if read(leader) = \perp then

wait-any()

36 end

// Invariant: leader \neq \bot. Next, signal out-neighbours in W.

37 foreach q \in W do

signal({q})

39 end

// Discover other out-neighbours.

40 foreach q \in \mathcal{P} \setminus \{\mathsf{PID}\}\ \mathbf{do}

if L2P[PID][q].LeaderElect() = lose then

X := X \cup \{q\}

42

end

43

44 end

// Signal discovered neighbours except those already signalled.

45 signal (X \setminus W)

// Share work in signalling chains of neighbours contacted at line 30.

46 foreach q \in U do in parallel

// Note: loop body executed concurrently for all q.

47 | wait(q)

48 end parallel

// All parallel calls to wait at line 47 completed by now. Ready to return.

```

Figure 5: Name consensus algorithm for the DSM model.

49 return read(leader)

means that q tried to contact p at line 30. If q did contact p, then q may rely on p to signal it when  $leader \neq \bot$ . Consequently, p determines the IDs of all such processes at lines 40–44, collects these IDs in the set X, and then signals them all at line 45. Processes participating in this signalling chain share work, which is necessary since there may be so many of them that p cannot directly communicate with all of them in a constant number of RMRs. The argument in p's call to signal at line 45 is actually the set difference  $X \setminus W$  and not X itself, which is done for two reasons: First, is efficiency – since p already called signal( $\{q\}$ ) for each process  $q \in W$  at line 38, it is not necessary to signal these processes again. The second reason is to meet the conditions of Lemma 3.12 – process p may not call signal twice with arguments that are non-disjoint sets, as this may break the two signalling chains.

Finally, p does its share of the work for each of the signalling chains it entered by contacting a neighbour at line 30. Each of these neighbours will try to signal p that  $leader \neq \bot$  by calling (via signal), and will rely on p calling wait to assist in the signalling mechanism. Thus, p calls wait(q) for each  $q \in U$  at line 47. More precisely, p executes a parallel for loop at lines 46–48, which makes multiple calls to wait in parallel by interleaving the corresponding operations, say in round-robin fashion. (We introduce parallelism here only to facilitate exposition. We could equally well use a modified version of wait that waits on multiple processes, but such a subroutine is somewhat more difficult to specify and analyze.) Note that p cannot wait for each  $q \in U$  sequentially because if p were to block inside a particular call to wait(q), p could prevent progress in the signalling chain corresponding to some other process in U, leading to deadlock. If p reaches line 49, then all the parallel calls have terminated, and  $leader \neq \bot$  holds (and has held since p reached line 37). Thus, NameDecide() returns the leader's ID to p.

To prove the correctness of NameDecide() (see Theorem 3.19 at the end of this section), we first establish some technical lemmas.

**Lemma 3.13.** Let H be any history of  $\mathcal{A}_{NC\text{-}DSM}$  in which Condition 3.1 holds, and every active process has completed the call to  $\hat{L}$ .LeaderElect() at line **26**. For any pair of distinct processes  $p, q \in \mathcal{P}$ , if p reads a value written by q while calling  $\hat{L}$ .LeaderElect() in H, then once p completes this call,  $q \in R_p$  or  $p \in W_q$ .

*Proof.* If, while executing line **26**, p reads remotely a value written by q, then p adds q to  $R_p$ . Otherwise, p reads a value written by q in p's local memory, in which case q adds p to  $W_q$ , because p and q are distinct.

**Lemma 3.14.** Let H be any history of  $\mathcal{A}_{NC\text{-}DSM}$  where Condition 3.1 holds, and every active process has completed the call to  $\hat{L}$ .LeaderElect() at line **26**. Suppose that the call to  $\hat{L}$ .LeaderElect() that ends last does so in step i of H. Let  $G_H$  denote the directed graph (V, E) where V is the set of process IDs and for any  $p, q \in V$ ,  $(p, q) \in E$  iff  $p \in R_q$  or  $q \in W_p$  in state H[i] (and thereafter). Let l denote the process elected leader at line **26**. Then, every process p active in H is reachable from l in  $G_H$ .

Proof. Suppose, by way of contradiction, that there is some process p active in H that is not reachable from l in  $G_H$ . Let R be the set of vertices of  $G_H$  that are reachable from l, and let  $\bar{R}$  be the remaining vertices. Note that  $l \in R$  and  $p \in \bar{R}$ , so both sets are nonempty. Our key observation is that  $H|\bar{R}$ , like H, is a history where each process in  $\bar{R}$  calls NameDecide() at most once. This is because by Lemma 3.13 and our definition of  $\bar{R}$ , no process  $q \in \bar{R}$  reads (in H or in  $H|\bar{R}$ ) from a shared variable a value written by a process in R. (If this were false, there would be an edge in  $G_H$  from a vertex in R to a vertex in  $\bar{R}$ , contradicting our definition of these sets.) Moreover,  $H|\bar{R}$  is a history of NameDecide() in which every active process completes its call to  $\hat{L}$ .LeaderElect() at

line 26, and receives the same response as in H. It follows from Specification 3.5 and Lemma 3.7 (a) that this response in H is lose for every process different from l, which contradicts Lemma 3.7 (a) for  $H|\bar{R}$  because l is not active in  $H|\bar{R}$  by our definition of  $\bar{R}$ . (Since l is reachable from itself, it belongs in R and not  $\bar{R}$ .)

**Lemma 3.15.** Let H be any history of  $\mathcal{A}_{NC\text{-}DSM}$  where Condition 3.1 holds. If some process has reached line **37** in some prefix H' of H, then leader  $\neq \bot$  holds in H after the prefix H'.

Proof. First, note that leader is written at most once during H, namely at line 27 by the process elected leader using  $\hat{L}$ . Consequently, the property  $leader \neq \bot$  is stable in H. It remains to show that for any process p, if p reaches line 37 then  $leader \neq \bot$ . Suppose, for contradiction, that this is false; without loss of generality let p be the first process to reach line 37 while  $leader = \bot$  in H. A fortiori,  $leader = \bot$  when p reached line 34, and therefore p completed a call to wait-any() at line 35. By Lemma 3.10 (d), some process q previously called signal(p) with  $p \in P$ . Since q calls signal only after it reaches line 37, it follows that q reached line 37 before p, and therefore while  $leader = \bot$ . This contradicts the definition of p as the first process to reach line 37 while  $leader = \bot$ .

**Lemma 3.16.** Let H be any history of  $\mathcal{A}_{NC\text{-}DSM}$  where Condition 3.1 holds. The following hold in H:

- (a) For any processes p and q, the LE algorithm L2P[p][q] is accessed according to Condition 3.4 and Condition 3.8.

- (b) If H is fair, all executions of signal at line 45 satisfy all the hypotheses of Lemma 3.12.

*Proof.* Part (a): It suffices to show that the two-process LE algorithm L2P[p][q] is executed at most once by p, at most once by q, and only with  $p \neq q$ . The only two places where L2P[p][q] is executed are line 30 and line 41. Thus, it follows from the loop conditions at line 29 and line 40 that if L2P[p][q] is accessed, then  $p \neq q$ . (At line 30, this is because  $z \notin R_z$  for any process z, by construction of the set R.) It also follows from the loops containing line 30 and line 41 that only p and q execute L2P[p][q], at most once at each line. If p or q executes L2P[p][q] at both lines, then this implies p = q, which contradicts our earlier observation.

Part (b): Consider a call to signal(P) made by some process q at line 45. To satisfy the hypotheses of Lemma 3.12, we must show two things: (1) q does not make another call to signal(P'), where  $P \cap P' \neq \emptyset$ ; and (2) every process  $p \in P$  eventually makes a call to wait(q) at line 47, provided that any prior call it makes to wait-any at line 35 terminates. For (1), note that any other such call to signal(P') by q must have been at line 38, and in that case P' is a singleton set containing an element of  $W_q$ . Then it follows from the set subtraction  $X \setminus W$  at line 45 that  $P \cap P' = \emptyset$ , as wanted. For (2), consider any  $p \in P$ . Note that since  $p \in P$  and by part (a) of this lemma, p must have contacted q at line 30 by Specification 3.5 and the algorithm. Thus, p is active. Furthermore, since H is fair, it follows from Lemma 3.16 (a), Specification 3.6, Lemma 3.10 (b), and the algorithm that p either makes a non-terminating call to wait-any at line 35, or reaches line 46. In the latter case, p begins the for loop at lines 46–48, where it makes a call to wait(p) for each p0. Since these calls are made in parallel, and since p1. We cause p2 contacted p2 at line 30, p3 eventually makes a call to wait(p3, as wanted. (Note that if a non-parallel for loop was used, p3 might become blocked in some other call to wait before calling wait(p1.)

**Lemma 3.17.** For any history H of  $\mathcal{A}_{NC\text{-}DSM}$  where Condition 3.1 holds, each call to NameDecide() terminates.

*Proof.* Suppose, for contradiction, that NameDecide() does not terminate for a subset B of processes that are active in H. By Lemma 3.7 (a), Specification 3.6, and fairness of H, every process active in H eventually completes its call to  $\hat{L}$ .LeaderElect() at line 26. Let  $G_H$  be the directed graph corresponding to H, as defined in the statement of Lemma 3.14. Let l be the process that is elected leader at line 26 during H. By Lemma 3.14, there is a directed path in  $G_H$  from l to every process in B.

Now choose any process  $p \in B$ . Since H is fair, it follows from the structure of NameDecide() that p makes progress until it makes a non-terminating call to LeaderElect, signal, wait-any, or wait. Every active process completes line 26, as argued earlier. All executions of the two-process leader election algorithm also terminate by Lemma 3.16 (a) and Specification 3.6. All executions of signal terminate by Lemma 3.10 (b). Thus, it remains to rule out the following two cases:

Case A: p makes a non-terminating call to wait-any at line 35. Since p reached line 35, it follows from the algorithm, particularly lines 26–27 and the test at line 34, that  $p \neq l$ . Now without loss of generality, assume that p is chosen so that the length of the path from l to p in  $G_H$  is minimal, and let z be p's upstream neighbour on this minimal path. Since there is an edge from z to p in this path, z is active by our definition of  $G_H$  (i.e., either z wrote a variable local to p, or p read a remote variable written by z). Moreover,  $z \in R_p$  or  $p \in W_z$ .

Subcase A-i:  $z \in R_p$ . First, we will show that p contacted z at line 30. Suppose otherwise. Then by the time p evaluates the condition at line 34, z has already reached line 41 by Lemma 3.16 (a) and Specification 3.5. Consequently, Lemma 3.15 implies that  $leader \neq \bot$  holds when p is at line 34. But this contradicts p branching to line 35 as stated in Case A. Thus, p contacts z, which implies (by Lemma 3.16 (a) and Specification 3.5) that z loses L2P[z][p] at line 41. Consequently, z adds p to  $X_z$  at line 42, and then calls  $signal(X_z \setminus W_z)$  at line 45, where  $p \in X_z \setminus W_z$  unless z already called signal(p) at line 38. In either case, p's call to wait-any at line 35 terminates by Lemma 3.12 and Lemma 3.16 (b), which contradicts the hypothesis of Case A.

Subcase A-ii:  $p \in W_z$ . Since z is active, and since it terminates in H by our selection of p, it follows that z calls signal( $\{p\}$ ) at line 38. In that case, p's execution of wait-any at line 35 terminates by Lemma 3.11 (b), which contradicts the hypothesis of Case A.

Case B: p makes a non-terminating call to wait(q) at line 47 for some process q. Note that p contacted q at line 30 since  $q \in U_p$  when p is at line 46. Now consider q. Since  $q \in R_p$ , p read a value written by q in H, and so q is active in H. Furthermore,  $q \neq p$ , and by our prior analysis (up to and including Case A), q eventually reaches line 46. Since p contacted q and  $p \neq q$ , it follows from Lemma 3.16 (a) and Specification 3.5 that q loses L2P[q][p].LeaderElect() at line 41 and so  $p \in X_q$  when q reaches line 46. Consequently, either  $p \in W_q$  and q completed a call to signal( $\{p\}$ ) at line 38, or  $p \notin W_q$  and q completed a call to signal( $\{p\}$ ) at line 45 with  $p \in X_q \setminus W_q$ . In either case, p's call to wait(q) at line 47 terminates by Lemma 3.12 and Lemma 3.16 (b), which contradicts the hypothesis of Case B.

**Lemma 3.18.** For any history H of  $\mathcal{A}_{NC\text{-}DSM}$  where Condition 3.1 holds, each call to NameDecide() incurs O(1) RMRs in the DSM model.

*Proof.* Let p be any process that calls NameDecide(). We will show that p performs O(1) RMRs in this call. We consider each line of NameDecide() where p may incur one or more RMRs, and argue that the number of RMRs p incurs at each such line is O(1).

- lines 26–28: The call to  $\tilde{L}$ .LeaderElect() incurs O(1) RMRs by Lemma 3.7 (b). At most one additional RMR occurs at line 27.

- lines 29–33: The loop here has  $|R_p|$  iterations, where  $|R_p| \in O(1)$  by Lemma 3.7 (c). RMRs

may occur only at line 30, and each execution of this line incurs O(1) RMRs by the RMR complexity of the two-process leader election algorithm, and by Lemma 3.16 (a).

- lines 34-36: There is at most one RMR at line 34, and the call to wait-any at line 36 incurs zero RMRs by Lemma 3.10 (a).

- lines 37–39: Each of these lines is executed  $|W_p|$  times, where  $|W_p| \in O(1)$  by Lemma 3.7 (c). Here RMRs occur only at line 38, and each execution of signal incurs O(1) RMRs by Lemma 3.10 (a).

- lines 40–44: The loop here has N iterations. RMRs may occur only at line 41, and in fact an execution of L2P[p][q].LeaderElect() by any process p, for any q, incurs zero RMRs by Specification 3.9 and Lemma 3.16 (a).

- line 45: The call to signal here incurs O(1) RMRs by Lemma 3.10 (a).

- lines 46–48: Each of these lines is executed  $|U_p|$  times, which is O(1) since  $U_p \subseteq R_p$  by the algorithm, and since  $|R_p| \in O(1)$  by Lemma 3.7 (c). Here RMRs occur only at line 47, where each execution of wait incurs O(1) RMRs by Lemma 3.10 (a).

• line 49: At most one RMR occurs here.

**Theorem 3.19.** For any history H of  $\mathcal{A}_{NC\text{-}DSM}$  (Figure 5) where Condition 3.1 holds, H satisfies Specifications 3.2 and 3.3. Furthermore, each call to NameDecide() in H incurs O(1) RMRs in the DSM model.

*Proof.* Consider any history H of  $\mathcal{A}_{NC-DSM}$  where Condition 3.1 holds.

**Specification 3.2:** Suppose that each call to NameDecide() terminates in H. It follows from the algorithm and Lemma 3.15 that NameDecide() returns to each caller the ID of the process l that wins  $\hat{L}$  at line 26. By Lemma 3.7 (a), l is the ID of a process that called  $\hat{L}$ .LeaderElect() in H, hence also called NameDecide(), as wanted.

**Specification 3.3:** Suppose that H is fair. Then each call to NameDecide() in H terminates by Lemma 3.17.

RMR complexity: This follows directly from Lemma 3.18.

### 4 Pseudo-Locks

In this section, we define a new building block called a pseudo-lock, which underlies the implementations presented in later sections. We then show how to construct pseudo-locks using name consensus, reads and writes at a cost of O(1) RMRs per process in the CC and DSM models.

Informally, a pseudo-lock is similar to a "one-shot" mutex, where at most one process acquires the critical section [10]. In addition, in a pseudo-lock any process that fails to acquire the CS must wait for the process that succeeded to leave the CS. Formally, a pseudo-lock is an algorithm that consists of two functions: an *entry protocol*, denoted Pseudo-Enter(), and an *exit protocol*, denoted Pseudo-Exit(). The two functions must be accessed according to the following etiquette:

#### Condition 4.1.

- (a) Each process calls Pseudo-Enter() and Pseudo-Exit() at most once.

- (b) A process can call Pseudo-Exit() only after completing a call to Pseudo-Enter().

The correctness properties of a pseudo-lock are captured in Specifications 4.2–4.3.

**Specification 4.2** (safety). For any history where Condition 4.1 holds:

- (a) If Pseudo-Enter() terminates, it returns a Boolean. If Pseudo-Exit() terminates, it returns OK.

- (b) Pseudo-Enter() returns true to at most one process.

- (c) If Pseudo-Enter() returns false to some process, then some other process has completed a call to Pseudo-Enter() with response true and subsequently made a call to Pseudo-Exit().

**Specification 4.3** (liveness). For any fair history where Condition 4.1 holds:

- (a) If at least one call to Pseudo-Enter() is made, then at least one such call terminates.

- (b) If some process calls Pseudo-Enter() with response true and then completes a call to Pseudo-Exit(), then all calls to Pseudo-Enter() terminate.

- (c) Every call to Pseudo-Exit() terminates.

**Definition 4.4.** We say that a process acquires the pseudo-lock if it makes a call to Pseudo-Enter() with response true. We say that a process fails to acquire the pseudo-lock if it makes a call to Pseudo-Enter() with response false.

In the remainder of this section, we present O(1)-RMR pseudo-lock implementations for the CC and DSM models.

### 4.1 Pseudo-locks in the CC Model

A pseudo-lock is straightforward to implement in the CC model given an O(1)-RMR name consensus algorithm, such as the one described in Section 3. One implementation is presented in Figure 6. (A very similar algorithm can be devised using leader election instead of name consensus, but we use name consensus nevertheless for consistency with the DSM algorithm.) Let  $\mathcal{A}_{PL-CC}$  denote the corresponding concurrent system.

```

Declarations

Shared variables: (global)

flag - Boolean, initially false

Subroutines: (global)

NameDecide() - O(1)-RMR name consensus algorithm (see Section 3)

Private variables: (per-process)

winner - process ID, uninitialized

```

```

Function Pseudo-Enter()

Function Pseudo-Exit()

Output: Boolean

// Note:

winner is assigned at

50 \ winner := NameDecide()

line 50 of Pseudo-Enter.

if winner = PID then

57 if winner = PID then

\mathbf{52}

return true

\mathbf{write}\ \mathit{flag} := \mathsf{true}

53 else

59 end

await flag = true

54

60 return OK

return false

56 end

```

Figure 6: Pseudo-lock for the CC model.

**Theorem 4.5.** For any history H of  $\mathcal{A}_{PL-CC}$  where Condition 4.1 holds, Specifications 4.2 and 4.3 hold. Furthermore, each call to Pseudo-Enter() or Pseudo-Exit() incurs O(1) RMRs in the CC model.

*Proof.* The proof is straightforward and is deferred to Appendix A.1.

#### 4.2 Pseudo-lock Implementation for the DSM Model

A pseudo-lock is straightforward to implement in the DSM model given an O(1)-RMR name consensus algorithm, such as the one described in Section 3, multiple instances of a two-process leader election algorithm that can be made local to one process (see Section 3.3), and the functions signal/wait from Section 3.4. One implementation is presented in Figure 7. Let  $\mathcal{A}_{PL-DSM}$  denote the corresponding concurrent system.

**Theorem 4.6.** For any history H of  $\mathcal{A}_{PL-DSM}$  where Condition 4.1 holds, Specifications 4.2 and 4.3 hold. Furthermore, each call to Pseudo-Enter() or Pseudo-Exit() incurs O(1) RMRs in the DSM model.