# **Recoverable Mutual Exclusion**

Wojciech Golab · Aditya Ramaraju

Received: September 2016 / Revision 1: September 2018 / Revision 2: September 2019 / Accepted: October 2019

Abstract Mutex locks have traditionally been the most common mechanism for protecting shared data structures in concurrent programs. However, the robustness of such locks against process failures has not been studied thoroughly. The vast majority of mutex algorithms are designed around the assumption that processes are reliable, meaning that a process may not fail while executing the lock acquisition and release code, or while inside the critical section. If such a failure does occur, then the liveness properties of a conventional mutex lock may cease to hold until the application or operating system intervenes by cleaning up the internal structure of the lock. For example, a process that is attempting to acquire an otherwise starvation-free mutex may be blocked forever waiting for a failed process to release the critical section. Adding to the difficulty, if the failed process recovers and attempts to acquire the same mutex again without appropriate cleanup, then the mutex may become corrupted to the point where it loses safety, notably the mutual exclusion property. We address this challenge by formalizing the problem of recoverable mutual exclusion, and proposing several solutions that vary both in their assumptions regarding hardware support for synchronization, and in their ef-

W. Golab

A. Ramaraju

Department of Electrical and Computer Engineering University of Waterloo, Canada E-mail: a2ramaraju@uwaterloo.ca ficiency. Compared to known solutions, our algorithms are more robust as they do not restrict where or when a process may crash, and provide stricter guarantees in terms of efficiency, which we define in terms of remote memory references.

Keywords mutual exclusion  $\cdot$  fault tolerance  $\cdot$  recovery  $\cdot$  concurrency  $\cdot$  synchronization  $\cdot$  shared memory  $\cdot$  non-volatile main memory  $\cdot$  multi-core algorithms  $\cdot$  durable data structures

### **1** Introduction

Concurrent programs running on multi-core architectures empower essential applications and services today, ranging from mundane desktop computing to massive back-end infrastructures that drive web search, ecommerce, and online social networks. Mutex locks have traditionally been the most popular mechanism for protecting shared data structures in concurrent programs owing to their simplicity: any sequential data structure can be made thread-safe by protecting operations on the data structure using a critical section. Mutual exclusion is therefore one of the oldest problems addressed in the literature on shared memory synchronization, starting with Dijkstra's seminal paper [12]. Over decades of research, locks have evolved from simple two-process algorithms to scalable mechanisms that provide elaborate correctness properties, such as fairness and local spinning [4]. One technical aspect of mutual exclusion, however, has remained nearly constant: a typical mutex lock cannot survive the failure of even one process while it is accessing the lock.

Failures in concurrent programs are an increasingly important reality, and may arise in several ways. For example, individual processes or threads of control in a

This research is supported in part by the Natural Sciences and Engineering Research Council (NSERC) of Canada, Discovery Grants Program; the Ontario Early Researcher Awards Program; and the Google Faculty Research Awards Program.

Department of Electrical and Computer Engineering University of Waterloo, Canada E-mail: wgolab@uwaterloo.ca

| Sec. | Algorithm                            | Failure-Free   | Worst-Case           | Synchronization      |

|------|--------------------------------------|----------------|----------------------|----------------------|

| Dec. | Algorithm                            |                |                      | ~                    |

|      |                                      | RMR Complexity | RMR Complexity       | Primitives Used      |

| 3.1  | two out of $N$ processes             | O(1)           | O(1)                 | reads and writes     |

| 3.3  | N-process arbitration tree           | $O(\log N)$    | $O(\log N)$          | reads and writes     |

| 4.1  | N-process base mutex (conventional)  | same as        | grows with the       | same as base mutex   |

|      | $\rightarrow$                        | base mutex     | number of failures   | +                    |

|      | N-process target mutex (recoverable) |                | (unbounded)          | reads and writes     |

| 4.2  | target mutex from Sec. 4.1           | same as        | O(N) when base mutex | same as base mutex   |

|      | $\rightarrow$                        | base mutex     | from Sec. 4.1 incurs | from Sec. 4.1        |

|      | N-process recoverable mutex          | in Sec. 4.1    | O(N) RMRs and        | + reads, writes, and |

|      | with bounded RMR complexity          |                | uses $O(N)$ space    | Compare-And-Swap     |

Fig. 1 Summary of recoverable mutual exclusion algorithms with respect to remote memory reference (RMR) complexity and required synchronization primitives.

program may terminate abruptly due to software bugs or deadlock resolution mechanisms. Similarly, processes may be affected by a loss of electrical power or faulty interconnect, especially in large-scale multiprocessor architectures that incorporate multiple system boards connected by a complex network of electronic and optical components. The straightforward approach to dealing with such failures is to shut down the entire program and restart it, which destroys all in-memory data structures in the program's address space, forcing recovery from slow secondary storage. In comparison, recovery by repairing in-memory data structures directly, as opposed to rebuilding them, is potentially much less disruptive as it by passes secondary storage altogether. This style of recovery is especially well suited to forthcoming hardware architectures that incorporate nonvolatile main memory (NVRAM) [16,41,42,44], which allows in-memory data structures to survive power failures. NVRAM collapses main memory and secondary storage into a single layer in the memory hierarchy, and makes it possible to use data structure repair to deal with both system-wide failures arising from power loss and partial failures arising from software bugs or hardware faults. In contrast, conventional systems with dynamic random-access memory (DRAM) must fall back on secondary storage to recover from power loss even if they implement data structure repair to deal more efficiently with partial failures, which increases software complexity.

Restoring a data structure protected by a mutex lock following a failure entails solving two technical problems: (1) completing or rolling back any actions in the critical section that may have been interrupted by the failure; and (2) repairing the internal state of the lock, if needed, to preserve safety and liveness. The first problem is arguably much easier because the critical section entails sequential reading and writing, and can be solved using database systems techniques [22]. The second problem involves more intricate lock acquisition and release code that deals with race conditions. If a process crashes while executing this code, then the liveness properties of a conventional mutex lock may cease to hold until the lock is repaired. For example, a process that is attempting to acquire an otherwise starvationfree mutex lock may be blocked forever, waiting for a crashed process to release the critical section. Adding to the difficulty, if the failed process recovers and attempts to acquire the same mutex again without appropriate cleanup, then the mutex may be corrupted to the point where it loses safety, particularly the mutual exclusion property.

Prior work on recoverable locking overcomes the inherent technical difficulty of the problem by introducing simplifying assumptions into the model of computation. Lamport and Taubenfeld define models where a process failure affects the values of shared variables in welldefined ways, for example by resetting any single-writer shared registers owned by the failed process [34, 48]. Bohannon, Lieuwen, and Silberschatz, as well as Bohannon, Lieuwen, Silberschatz, Sudarshan, and Gava, focus instead on algorithms with multi-writer variables, and assume that the operating system provides failure detection [8,9]. In their approach, the internal state of the lock is repaired carefully by a reliable centralized recovery process that executes concurrently with the lock acquisition and release protocols. Our approach similarly allows multi-writer variables, but deals with failure detection and recovery in a more abstract way by assuming that a failed process is revived eventually and given an opportunity to participate in recovery. Specifically, recovery actions are integrated into the lock acquisition code, where they are exposed to both concurrency and failures.

The contributions in this paper begin with a formal definition of recoverable mutual exclusion with respect to our crash-recovery failure model. We then present a collection of recoverable mutex algorithms, whose properties are summarized in Figure 1. We start with a two-process solution in Section 3.1 that uses atomic read and write operations only, then progress to an N-process solution in Section 3.3 also using reads and writes, and finally present a pair of algorithms in Sections 4.1–4.2 that can transform any conventional mutex ("base mutex") into a recoverable mutex ("target mutex") while preserving efficiency in the absence of failures. The latter transformation can be used to add recoverability to efficient queue-based locks (e.g., MCS [39]).

# 2 Model

We consider N asynchronous unreliable processes, labeled  $p_1, p_2, \ldots, p_N$ , that communicate by accessing variables in shared memory. These processes compete for an exclusive lock (mutex), which can be used to protect a shared resource, by following the execution path illustrated in Algorithm 1. At initialization, as well as immediately after crashing, a process is in the remainder section (RS), where it does not access the lock. Upon leaving the RS, a process always executes the recovery section, denoted by the procedure **Recover**(). This is where the process cleans up the internal structure of the lock, if needed, following a crash failure. Next, a process attempts to acquire the lock in the *entry section*, denoted by the procedure **Enter**(). The entry section is sometimes modeled in two parts: a bounded<sup>1</sup> section of code called the *doorway* that determines the order in which processes acquire the lock, followed by a *wait*ing room, where processes wait for their turn.<sup>2</sup> Upon completing the entry section, a process has exclusive accesses to the *critical section* (CS). A process subsequently releases the lock by executing the *exit section*, denoted by the procedure **Exit**(), and finally transitions back to the RS.

Our model intentionally defines a sequential flow of control in which processes always execute code in the order prescribed by Algorithm 1: RS, **Recover**(), **Enter**(), CS, and **Exit**(). This convention follows naturally from the assumption that **Recover**(), **Enter**() and **Exit**() are procedures that are called by an application and punctuated by application-specific code (e.g., the RS and CS), rather than sections of a contiguous algorithm.<sup>3</sup> Branches from the code of one procedure

<sup>3</sup> In a practical implementation, the code of  $\mathbf{Recover}()$  and  $\mathbf{Enter}()$  can be packaged in a single procedure for simplicity.

to the code of a different procedure are not permitted because in practice one procedure must return control to the application (i.e., pop a stack frame) before the application invokes the next procedure in the sequence. For example, a process that has no recovery actions to perform can branch from the beginning of **Recover**() to the end, skipping the body of the recovery section, but a process that is recovering from a failure in **Exit**() cannot branch from **Recover**() directly to **Exit**() and skip the application-specific CS code.

The boundary between the recovery and entry sections in Algorithm 1 is determined by the position of the doorway within an algorithm. That is, the recovery section ends prior to the first step of the doorway, which defines the start of the entry section. The separation of code into explicit recovery and entry sections makes it possible to define the doorway as a prefix of the entry section, as in conventional mutual exclusion. On the other hand, the recovery section has no formal significance in algorithms that lack doorways entirely.

#### loop forever

| Remainder Section (RS)                                                             |

|------------------------------------------------------------------------------------|

| $\mathbf{Recover}()$                                                               |

| $\mathbf{Enter}() \begin{cases} \text{Doorway} \\ \text{Waiting Room} \end{cases}$ |

| Critical Section (CS)                                                              |

| $\mathbf{Exit}()$                                                                  |

Algorithm 1: Execution path of a process participating in recoverable mutual exclusion. A crash failure reverts a process back to the RS.

Correctness properties for mutex algorithms are expressed in reference to *histories* that record the actions of processes as they execute the pseudo-code of Algorithm 1. Formally, a history H is a sequence of steps that come in two varieties: ordinary steps and crash steps. An ordinary step is a shared memory operation combined with local computation such as arithmetic operations, accessing one or more private variables, and advancing the program counter. A crash step denotes a process failure that resets the private variables of a process to their initial values. Each process has a program counter, which is a private variable that identifies the next ordinary step a process is poised to take. The program counter points to the RS initially, and is updated in each step. We say that a process is  $at \ line \ X$ of an algorithm if its program counter identifies an ordinary step corresponding to line X of the algorithm's pseudo-code. One line of pseudo-code may entail multiple steps.

<sup>&</sup>lt;sup>1</sup> The term *bounded* in reference to a piece of code means that there exists a function f of the number of processes Nsuch that the code performs at most f(N) shared memory operations in all executions of the algorithm instantiated for N processes.

$<sup>^2\,</sup>$  As explained later on in the model near the discussion of First-Come-First-Served fairness, we assume that the doorway is well-defined and bounded only in a subset of execution histories that are relevant to our weaker notion of FCFS.

The next step a process takes after a crash is either another crash step, or the first step of **Recover**(). A process is said to *recover* following a crash step by executing the first step of **Recover**(). A passage is a sequence of steps taken by a process from when it begins **Recover**() to when it completes **Exit**(), or crashes, whichever event occurs first. We say that a process is *in cleanup* if it is executing **Recover**() following a passage that ended with a crash step. A passage is called *failure*free if it does not end with a crash step, which includes all incomplete passages. A *super-passage* is a maximal non-empty collection of consecutive passages executed by the same process where (only) the last passage in the collection is failure-free. A process is executing a super-passage if it is either outside the RS or in the RS following a crash failure. A process may execute the CS at most once per passage, and possibly multiple times in one super-passage.

A process that completes the CS and then crashes in **Exit**() is required in our model to continue taking steps until it completes a failure-free passage, which entails one or more additional and redundant executions of the CS. Although this behavior is somewhat inefficient, it simplifies the model conceptually by reducing the number of possible execution paths. Jayanti and Joshi [29] propose an alternative model of recovery that permits additional transitions among the different sections of a recoverable mutex, and opens the door to recovery without redundant executions of the CS in some scenarios. Their model allows a process that crashes in **Exit**() to transition from **Recover**() directly to the CS, to **Exit**(), or even to the RS. Informally speaking, such transitions might occur if the crash occurs at the beginning of, in the middle of, and at the end of **Exit**(), respectively.

A passage through a recoverable mutex algorithm may be influenced directly or indirectly by process failures. We formalize the notion of potential influence by reasoning precisely about interleaving among passages. We say that one passage *interferes* with another if their super-passages are concurrent, meaning that neither super-passage ends before the other begins. For any integer  $k \ge 0$ , we call a passage *k*-failure-concurrent if and only if:

- -k = 0 and the passage ends with a crash or begins in cleanup (i.e., the previous passage of the same process ended with a crash); or

- -k > 0 and the passage interferes with any passage (possibly itself) that is (k-1)-failure-concurrent.<sup>4</sup>

It follows easily that if a passage is k-failure-concurrent then it is also k'-failure-concurrent for any k' > k. In general, smaller values of k are preferred when the desired behavior of one process (e.g., a complexity bound) is conditioned on the absence of a k-failure-concurrent passage. This is because decreasing k tends to reduce the number of such k-failure-concurrent passages.

The set of histories generated by possible executions of a mutex algorithm is prefix-closed. For any finite history H, we denote the length of H (i.e., number of steps in H) by |H|. A history H is *fair* if it is finite, or if it is infinite and every process either executes zero steps, or halts in the RS after completing a failure-free passage, or executes infinitely many steps. We assume for simplicity of analysis that the critical section is bounded.

The correctness properties of our recoverable mutex algorithms are derived from Lamport's formalism [36], which considers only permanent crashes ("unannounced death") and Byzantine failures ("malfunctioning"). Differences between our definitions of correctness properties and Lamport's are highlighted in *italics* for clarity. Note that mutual exclusion, deadlock-freedom, and terminating exit are the only properties considered essential for correctness; the others are desirable but optional [4].

Mutual Exclusion (ME): For any finite history H, at most one process is in the CS at the end of H.

**Deadlock-Freedom (DF):** For any infinite fair history H, if a process  $p_i$  is in the recovery or entry section after some finite prefix of H, then eventually some process  $p_j$  (possibly  $j \neq i$ ) is in the CS, or else there are infinitely many crash steps in H.

**Starvation-Freedom (SF):** For any infinite fair history H, if a process  $p_i$  is in the recovery or entry section after some finite prefix of H, then eventually  $p_i$  itself enters the CS, or else there are infinitely many crash steps in H. (SF implies DF.)

**Terminating Exit (TE):** For any infinite fair history H, any execution of **Exit**() by a process  $p_i$  completes in a finite number of  $p_i$ 's steps, or else there are infinitely many crash steps in H.

Wait-Free Exit (WFE): For any history H, any execution of Exit() by a process  $p_i$  completes in a bounded number of  $p_i$ 's steps.

The DF and SF properties guarantee progress only in fair histories with finitely many crash steps, which allows for histories where every process takes infinitely many steps and yet no process enters the CS. Such histories must be included in the model because no algorithm can guarantee progress irrespective of the frequency of failures. Jayanti, Jayanti, and Joshi define a more stringent SF property that prevents starvation in executions that contain infinitely many failures pro-

$<sup>^4\,</sup>$  The term *cleanup-concurrent* defined in the conference version of this paper [20] is analogous to 1-failure-concurrent in this model.

vided that each process crashes only a finite number of times in each super-passage [30].

The SF and WFE properties are compatible with the algorithmic techniques introduced in this paper, and are either guaranteed or preserved by all our algorithms (see Theorems 1,3–6 for Algorithms 2–6, respectively).

Next, we introduce new properties to constrain the complexity of the recovery section:

Wait-Free Recovery (WFR): For any history H, any execution of Recover() by a process  $p_i$  completes in a bounded number of  $p_i$ 's steps.

*k*-Bounded Recovery (*k*-BR): For any history *H*, any execution of Recover() by a process  $p_i$  completes in a bounded number of  $p_i$ 's steps unless  $p_i$ 's passage is *k*-failure-concurrent.<sup>5</sup>

It is essential for a recoverable mutual exclusion algorithm to satisfy WFR or k-BR for some  $k \ge 0$ , which ensures that the recovery section is bounded in the absence of failures. It follows easily that WFR is strictly stronger than 0-BR, and that for any  $k \ge 0$  and k' > k, k-BR is strictly stronger than k'-BR. In any algorithm that satisfies WFR, the recovery code can be shifted to the entry section and joined with the doorway, although doing so weakens the FCFS and k-FCFS properties defined shortly by lengthening the doorway.

We also propose a pair of properties that simplify recovery from a crash failure inside the critical section, and make it possible to nest recoverable mutex locks:

**Critical Section Re-entry (CSR):** For any history H and for any process  $p_i$ , if  $p_i$  crashes inside the CS then no other process may enter the CS before  $p_i$  re-enters the CS after the crash failure under consideration.

Bounded Critical Section Re-entry (BCSR): For any history H and for any process  $p_i$ , if  $p_i$  crashes inside the CS then  $p_i$  incurs a bounded number of steps in each subsequent execution of the recovery and entry sections until it re-enters the CS.

**Lemma 1** If a recoverable mutex algorithm satisfies BCSR then it also satisfies CSR.

**Proof** Suppose that process  $p_i$  crashes inside the CS in step c of some history H of the mutex algorithm. Suppose for contradiction that H has a prefix G that includes c, and at the end of which some other process  $p_j$  has entered the CS, and yet  $p_i$  has not yet re-entered the CS after c in G. By the BCSR property, if  $p_i$  continues to takes steps after G then it re-enters the CS in a bounded number of its own steps by completing the recovery and entry sections. Let G' denote the extension of G where  $p_i$  has done so. Then G' is a finite history of the mutex algorithm at the end of which both  $p_i$  and  $p_j$  are in the CS simultaneously. This contradicts the mutual exclusion property of the algorithm, which is required for correctness.

Finally, we present definitions related to first-comefirst-served (FCFS) fairness. The standard definition of FCFS is given first for completeness:

**First-Come-First-Served (FCFS):** For any history H, suppose that process  $p_i$  completes the doorway in its  $\ell_i$ -th passage before process  $p_j$  begins the doorway in its  $\ell_j$ -th passage. Then  $p_j$  does not enter the CS in its  $\ell_j$ -th passage before  $p_i$  enters the CS in its  $\ell_i$ -th passage.

The above FCFS property is incompatible with the CSR property in the sense that a process may bypass the doorway and waiting room entirely while recovering from a failure in the CS, and so we introduce an alternative fairness property called *k*-FCFS.

*k*-First-Come-First-Served (*k*-FCFS): For any history *H*, suppose that process  $p_i$  begins its  $\ell_i$ -th passage and  $p_j$  begins its  $\ell_j$ -th passage. Suppose further that neither passage is *k*-failure-concurrent, and that process  $p_i$  completes the doorway in its  $\ell_i$ -th passage before process  $p_j$  begins the doorway in its  $\ell_j$ -th passage in *H*. Then  $p_j$  does not enter the CS in its  $\ell_j$ -th passage before  $p_i$  enters the CS in its  $\ell_i$ -th passage.

Intuitively, k-FCFS is a weakening of FCFS that ignores k-failure-concurrent passages, where processes may enter the CS out of order with respect to their execution of the doorway. In fact, the doorway can be undefined or unbounded in such passages since it is not relevant. (We adopt this approach in the transformations presented in Section 4.) It follows easily that FCFS is strictly stronger than 0-FCFS, and that for any  $k \ge 0$ and k' > k, k-FCFS is strictly stronger than k'-FCFS.

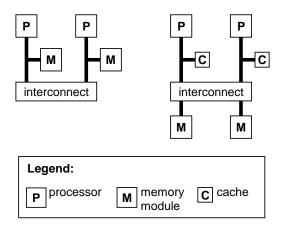

Aside from fundamental safety and liveness properties, we are interested in the efficiency of mutex algorithms, particularly with respect to the number of remote memory references (RMRs) executed by a process per passage. The precise definition of RMRs depends on the shared memory hardware architecture, and in this paper we consider both the cache-coherent (CC) and distributed shared memory (DSM) models [4], which are illustrated in Figure 2. In the CC model, any memory location can be made locally accessible to a process by creating a copy of it in the corresponding processor's cache. A distributed coherence protocol ensures that when a memory location is overwritten by one processor, cached copies held by other processors are either invalidated or updated. In contrast, the DSM model lacks (coherent) caches but allows each processor to locally

$<sup>^5\,</sup>$  The Bounded Recovery property defined in the conference version of this paper [20] is analogous to 1-BR in this model.

access a portion of the address space corresponding to its attached memory module.<sup>6</sup>

Fig. 2 Abstract models of shared memory architectures-DSM (left) and CC (right).

Loosely speaking, an RMR in the CC or DSM model is any memory operation that traverses the interconnect shown in Figure 2. In the CC model, we (conservatively) count each shared memory operation as an RMR with the exception of an *in-cache* read, which occurs when a process  $p_i$  reads a variable v that it has already read in an earlier step, following which step no process has accessed v except by a read operation. In the DSM model, each shared variable is local to exactly one process (assuming a one-to-one mapping between processes and processors), which is determined statically at initialization. A mutex algorithm is called *local* spin if its worst-case RMR complexity per passage is bounded.

# **3** Solutions Using Atomic Reads and Writes

Although modern multiprocessors support a variety of powerful read-modify-write primitives, algorithms that use only atomic reads and writes can be made recoverable more easily if they rely partially or wholly on single-writer shared variables. This is because updates to such variables are idempotent. Therefore, we first present two such algorithms, and then use them in Section 4 as building blocks of more advanced solutions that attain better RMR complexity in the absence of

failures by leveraging read-modify-write operations. Notably, the N-process algorithm described shortly in Section 3.3 is used to protect the recovery section of the algorithms presented later on in Section 4. We also present a transformation in Section 3.2 that adds the BCSR property to any recoverable mutex.

3.1 Algorithm for Two-of-N-Processes

# Shared variables:

- T: long process ID or  $\perp$ , initially  $\perp$

- C[...]: associative array indexed by left and right, each element a tuple of the form

$\langle \text{long process ID or } \perp, \text{integer} \rangle$ , each element initially  $\langle \perp, 0 \rangle$

P[1..N]: array of integer spin variables, element P[i]local to process  $p_i$  in the DSM model, initially all elements zero

#### **Definitions:**

$$- \text{ other}(side) = \begin{cases} \text{ left } & \text{if } side = \text{right} \\ \text{right } & \text{if } side = \text{left} \end{cases}$$

**Procedure Recover**(*side*) for process  $p_i$

- 1 if  $C[side] = \langle i, 1 \rangle$  then

- $\langle rival, ... \rangle := C[\mathsf{other}(side)]$  $\mathbf{2}$

- if  $rival \neq \bot$  then з P[rival] := 24

- 5 else if  $C[side] = \langle \perp, 2 \rangle$  then

- execute lines 19-22 of  $\mathbf{Exit}()$ 6

| Procedure | Enter | (side) | ) for | process | $p_i$ |

|-----------|-------|--------|-------|---------|-------|

|-----------|-------|--------|-------|---------|-------|

7  $C[side] := \langle i, 1 \rangle$ **8** T := i

**9** P[i] := 0

$\langle rival, ... \rangle := C[\mathsf{other}(side)]$ 10

- 11 if  $rival \neq \bot$  then if T = i then 12

- if P[rival] = 0 then 13

P[rival] := 1

- 14

- await P[i] > 115

| 10 | II I = i then    |

|----|------------------|

| 17 | await $P[i] = 2$ |

| Procedure                                 | Exit(  | (side) | ) for | process | $p_i$ |

|-------------------------------------------|--------|--------|-------|---------|-------|

| 1 I O O O G G G G G G G G G G G G G G G G | 10,100 | ouuc.  | , 101 | process | Pl    |

- 18  $C[side] := \langle \perp, 2 \rangle$

- 19 rival := T

- 20 if  $rival \notin \{i, \bot\}$  then

- P[rival] := 221

- **22**  $C[side] := \langle \perp, 0 \rangle$

Algorithm 2: Recoverable extension of Yang and Anderson's two-process mutex.

<sup>&</sup>lt;sup>6</sup> Despite the prevalence of cache-coherent architectures, the DSM model remains important in practice because of its inherent scalability. Intel's Single-chip Cloud Computer, for example, sacrifices cache-coherence "to simplify the design, reduce power consumption and to encourage the exploration of datacenter distributed memory software models" [26].

Our first algorithm is obtained by transforming Yang and Anderson's two-process local-spin mutex [49]. Like Yang and Anderson's algorithm, ours is designed for participation by two out of N processes at a time, meaning that at most two processes at a time execute a super-passage through the mutex. The execution paths of the two processes are distinguished by a special argument  $side \in \{\text{left}, \text{right}\}$  of the procedures **Recover**(), **Enter**(), and **Exit**(), which is used internally as the index of an associative array (e.g., see line 1). The rules regarding the values of the argument are two-fold:

- 1. A process must use the same value of *side* consistently in each super-passage; and

- 2. If two processes are executing super-passages concurrently then they must use distinct values of *side*.

We will use the notation  $side_i$  in reference to the value of the argument side for process  $p_i$  that is executing a super-passage at the end of a given finite history. The shorthand notation other(*side*) defined for convenience in Algorithm 2 denotes the "opposite side" to the one being used by a given process.

The recoverable two-process mutex is presented as Algorithm 2 for process  $p_i$ . There are three shared variables: T is used to break symmetry at line 8; C is an associative array used to track the progress of a process at lines 7, 18, and 22; and P is an array of spin variables used for busy-waiting at lines 15 and 17. The entry and exit sections generally follow the structure of Yang and Anderson's algorithm, but there are important differences: (i) the elements of array C, which hold the IDs of processes competing for the CS in the original algorithm, are augmented with an integer tag that indicates progress through a passage; and (ii) an additional write to C is added at line 22 of  $\mathbf{Exit}()$  so that a recovering process can detect whether it crashed in the exit section. In the body of **Enter**(), starting at line 7, a process proceeds directly to the CS unless it encounters a rival at line 11, in which case the busy-wait loop at line 15 ensures that both processes have progressed past line 8, and the second busy-wait loop at line 17 gives priority to the process that executed line 8 the earliest. **Exit**() checks for a rival at line 19, and hands over the critical section at line 21, if required.

The recovery section at lines 1–6 is a new addition, and is executed whenever a process transitions out of the RS. If process  $p_i$  is not in cleanup then  $C[side(i)] = \langle \perp, 0 \rangle$  holds while it executes **Recover**(), and so the conditions tested at lines 1 and 5 are both false. In that case,  $p_i$  proceeds directly to **Enter**(), which ensures bounded recovery. Otherwise,  $p_i$  tries to determine where it failed. Lines 1–4 handle a crash inside **Enter**() or the CS, in which case  $p_i$  determines at line 2 whether it has a rival  $p_j$ . If so, then  $p_i$  assigns P[j] := 2 at line 4 to ensure that the rival is not stuck at line 15 or 17 and then repeats the entry see

stuck at line 15 or 17, and then repeats the entry section. Lines 5–6 handle a crash inside  $\mathbf{Exit}()$ , in which case  $p_i$  repeats the body of the exit section and then proceeds to the entry section.

The remainder of this section presents the analysis of Algorithm 2. Theorem 1 asserts the main correctness properties: ME, SF, 0-BR, and O(1) worst-case RMR complexity in the CC and DSM models.

#### Lemma 2 Algorithm 2 satisfies mutual exclusion.

*Proof* Suppose for contradiction that distinct processes  $p_i$  and  $p_j$  are in the CS simultaneously at the end of some finite history H. Consider the order in which  $p_i$ and  $p_j$  execute line 8, where they write their ID into T in their final passages prior to entering the CS. Without loss of generality, suppose that  $p_j$  executes line 8 first (the other case is symmetric). Then  $p_i$  has already completed line 7 by the time  $p_i$  executes line 8. This implies that  $p_i$  later reads  $\langle j, 1 \rangle$  from  $C[\mathsf{other}(side)]$  at line 10. Therefore,  $p_i$  subsequently executes lines 12 and 16, where it reads *i* from *T*, and hence  $p_i$  proceeds to line 17, where it waits for P[i] = 2. Since we assume that  $p_i$  eventually enters the CS,  $p_j$  must write P[i] := 2at some point after  $p_i$  resets P[i] := 0 at line 9 and before  $p_i$  completes line 17. This is a contradiction because  $p_i$  completes line 8 before  $p_i$ , then completes **Enter**() and remains in the critical section up to the end of H. In particular,  $p_j$  does not execute line 4 of **Recover**() or line 21 of  $\mathbf{Exit}()$  after  $p_i$  completes line 9, and these are the only two lines where  $p_i$  may write P[i] := 2.  $\Box$

**Lemma 3** Let H be a finite history of Algorithm 2. If process  $p_i$  is executing a super-passage at the end of H and  $C[other(side_i)] = \langle j, ... \rangle$  then  $i \neq j$ .

Proof A process  $p_i$  writes its own ID into  $C[side_i]$  at line 7, and  $side_i$  does not change until  $p_i$  completes a super-passage, which entails executing the exit section and erasing i from C[side] at line 18. Since elements of C are initialized to  $\langle \perp, 0 \rangle$ , this implies that only  $C[side_i]$ may contain i while  $p_i$  is executing a super-passage. As a result, if  $C[other(side_i)]$  contains the ID  $j \neq \perp$  then  $j \neq i$ .

**Lemma 4** Let H be a history of Algorithm 2 and let  $p_i$  be any process. Let S be any contiguous subhistory of H in which  $p_i$  does not execute line 9. Then there is no step in S that decreases the value of P[i].

**Proof** In general P[i] only takes on the values 0, 1 and 2. Furthermore, only process  $p_i$  may assign P[i] := 0, which occurs at line 9. Therefore, if  $p_i$  does not execute

line 9 in S then P[i] can only decrease if it transitions from 2 down to 1 by the action of some rival process  $p_j$ . This may only happen at line 14, and only after  $p_j$ reads P[i] = 0 earlier at line 13. Since we assume that P[i] = 2 immediately before  $p_j$  assigns P[i] := 1, it follows that another process  $p_k$  assigns P[i] := 2 after  $p_i$ 's read at line 13 and before  $p_i$ 's write at line 14. This can only occur at line 21 of  $\mathbf{Exit}()$  after  $p_k$  reads T = iat line 19. Since the mutex is accessed by at most two processes at a time and since we assume that  $p_j$  is at line 14 at this point, either  $p_i$  or  $p_k$  is the last process to write T, and so  $p_i$  must be one of these two processes since T = i. It follows from line 20 that  $k \neq i$ , which implies that j = i. Thus,  $p_j$  reads its own ID from  $C[\mathsf{other}(side_j)]$  at line 10, which contradicts Lemma 3.

#### Lemma 5 Algorithm 2 satisfies starvation-freedom.

**Proof** Let H be a fair history with finitely many crash steps, and suppose for contradiction that some process  $p_i$  is in the recovery or entry section after some finite prefix of H, and does not subsequently enter the CS. Then in its final passage,  $p_i$  becomes stuck at line 15 or at line 17, where it busy-waits on P[i]. Without loss of generality, assume that  $p_i$  is the first such process to write T at line 8.

Since  $p_i$  reaches line 15 or line 17 in its last passage in H,  $p_i$  reads the ID of a rival process  $p_j$  from  $C[\mathsf{other}(side_i)]$  at line 10, where  $i \neq j$  by Lemma 3. Then  $C[\mathsf{other}(side_i)] = C[side_j] = \langle j, 1 \rangle$ , and so  $p_j$  is either executing a passage or is in the RS following a crash failure. Let s be the first step in the corresponding super-passage of  $p_j$ . Then  $C[side_j] = \langle \perp, 0 \rangle$  holds immediately after s, either by initialization or by the most recent execution of line 22 prior to s by a process that accessed the mutex with the same *side* as  $p_j$ 's. Subsequently,  $side_j$  does not change and either  $C[side_j] = \langle \perp, 0 \rangle$  or  $C[side_j] = \langle j, 1 \rangle$  holds until  $p_j$ reaches line 18. Since H is fair and contains finitely many crash steps, this implies that  $p_j$  eventually executes line 8 where it writes T := j. Let  $w_j$  be the last write of T at line 8 by  $p_i$  after s and before  $p_i$  completes a failure-free passage, and let  $w_i$  be the last write of T at line 8 by  $p_i$ , which occurs in  $p_i$ 's final passage where it becomes stuck.

Next, we show that  $p_j$  does not crash after  $w_j$  and before reaching line 18, which assigns  $C[side_j] := \langle \perp, 2 \rangle$ and erases  $p_j$ 's ID from  $C[side_j]$ . Suppose otherwise, and note that on recovery  $p_j$  assumes the same side as before the failure. Then  $C[side_j] = \langle j, 1 \rangle$  holds on recovery by  $p_j$ 's earlier execution of line 7, and continues to hold no matter how many times  $p_j$  crashes, until  $p_j$  reaches line 18. Since H is fair and contains finitely many crash steps,  $p_j$  eventually executes lines 7–8. In other words,  $p_j$  writes T again before completing a failure-free passage, which contradicts the definition of  $w_j$ . Thus,  $p_j$  does not crash before reaching line 18.

<u>Case A:</u>  $w_i$  occurs before  $w_i$ . Then by our careful choice of  $p_i$  as the first process to execute line 8 and then get stuck,  $p_i$  either crashes or enters the CS after  $w_i$ , but does not become stuck in this passage. As explained earlier,  $p_i$  does not crash after  $w_i$  and before reaching line 18, and so  $p_j$  completes **Enter**() without crashing. From this point onward,  $p_j$  proceeds to line 18 of **Exit**(). Thus,  $p_i$  eventually assigns  $C[side] := \langle \bot, 2 \rangle$  at line 18. Subsequently,  $p_i$  executes lines 19–22 of **Exit**(), either directly or by crashing, recovering, and executing line 6 of  $\mathbf{Recover}()$ . Now recall from the definition of steps s and  $w_i$  that  $p_i$  discovers  $p_i$  at line 10 in its final passage, and so it follows that  $p_i$  executes line 10 before  $p_j$  reaches line 18 of  $\mathbf{Exit}()$ , which erases  $p_j$ 's ID from  $C[side_j]$ . As a result,  $w_i$  occurs before  $p_j$  reads T in  $\mathbf{Exit}()$ , which ensures that  $p_i$  discovers  $p_i$  at line 19. At this point  $p_i$  has already executed line 9 for the last time, and so when  $p_i$  eventually assigns P[i] := 2 at line 21, it follows from Lemma 4 that the value of P[i]does not decrease in the remainder of H. This contradicts  $p_i$  busy-waiting forever for  $P[i] \ge 1$  at line 15 or P[i] = 2 at line 17.

<u>Case B</u>:  $w_j$  occurs after  $w_i$ . As explained earlier,  $p_j$  does not crash after  $w_j$  and before reaching line 18. Thus,  $p_j$  either reaches line 18 or becomes stuck in **Enter**() without crashing, in contrast to Case A where we know it does not become stuck by our careful choice of  $p_i$ . Now consider  $p_j$ 's execution of **Enter**() following step  $w_j$  at line 8.

<u>Subcase B1:</u>  $p_i$  is stuck at line 15 waiting for  $P[i] \ge 1$ . In this case  $p_i$  must read T = i at line 12 before  $w_j$ , as otherwise  $w_j$  overwrites T with  $j \ne i$ . As a result,  $p_i$  assigns P[i] := 0 at line 9 also before  $w_j$ , and this is the last such write in H. Next,  $p_j$  performs  $w_j$  at line 8 and reads T = j at line 12 since  $w_j$  occurs after  $w_i$ . Then, either  $p_j$  reads  $P[i] \ne 0$  at line 13 or it reads P[i] = 0 and then assigns P[i] := 1 at line 14. In both cases  $P[i] \ge 1$  holds, and the value of P[i] does not decrease in the remainder of H by Lemma 4. This contradicts the hypothesis of Subcase B1.

<u>Subcase B2:</u>  $p_i$  is stuck at line 17 waiting for P[i] = 2. In this case  $p_i$  reads  $P[i] \ge 1$  earlier at line 15 after assigning P[i] := 0 at line 9, which is the last such write in H. Thus, another process  $p_k, k \ne i$ , overwrites P[i]with a positive value between  $p_i$ 's final executions of lines 9 and 15. Let  $w_k$  be  $p_k$ 's write to T at line 8 in this passage. It follows that  $w_k$  precedes  $w_i$ , as otherwise  $p_i$  would not observe T = i at line 16 after completing line 15 and before reaching line 17 because  $w_i$  is the last step in H where  $p_i$  assigns T := i. Thus,  $w_k$  precedes  $w_j$  as well under the hypothesis of Case B, and so  $p_k$  is either  $p_j$  or some process that returns to the RS before  $p_j$  begins its passage leading to  $w_j$ . Since  $p_k$ 's write to P[i] occurs after  $p_i$  discovers  $p_j$  at line 10 in its final passage, it follows in fact that k = j and that  $w_k$  is part of  $p_j$ 's super-passage that starts at step s.

Thus, we have shown that  $p_j$  writes T at line 8 at least twice in the super-passage starting at step s: first in  $w_k$ , which occurs before  $w_i$ , and then in  $w_j$ , which occurs after  $w_i$ . Since both writes occur in the same superpassage, this implies that  $p_j$  crashes outside the RS with  $C[side_j] = \langle j, 1 \rangle$  or  $C[side_j] = \langle \perp, 2 \rangle$ , and returns to **Enter**() after recovering. Next, consider  $p_i$ 's write of P[i] in the passage containing step  $w_k$ , where we argued that  $p_i$  assigns a positive value to P[i]. This write must occur at line 14, as otherwise it assigns P[i] := 2and this value does not decrease in the remainder of H by Lemma 4. Moreover, this write occurs between  $p_i$ 's final executions of lines 9 and 15, hence after  $p_i$ 's write  $w_i$  to T at line 8. Therefore,  $p_j$ 's passage containing  $p_i$ 's second write  $w_i$  begins after  $w_i$ , and also after  $p_i$  writes its ID to  $C[side_i]$  at line 7. Now consider  $p_i$ 's execution of **Recover**() in the latter passage, in which  $C[side_j] = \langle j, 1 \rangle$  or  $C[side_j] = \langle \perp, 2 \rangle$  holds initially. If  $p_j$  recovers with  $C[side_j] = \langle j, 1 \rangle$  then it reads  $p_i$ 's ID from  $C[side_i]$  at line 2, and then assigns P[i] := 2 at line 4. Otherwise, if  $p_j$  recovers with  $C[side_j] = \langle \perp, 2 \rangle$ then  $p_i$  executes line 5, which in turn executes lines 19– 22 of  $\mathbf{Exit}()$ . Here process  $p_j$  reads the ID of  $p_i$  from T, and then assigns P[i] := 2 at line 19. In both cases,  $p_j$ 's write to P[i] occurs after  $p_i$ 's last execution of line 8, and so it follows from Lemma 4 that the value of P[i]does not decrease in the remainder of H, which contradicts the hypothesis of Subcase B2.

**Lemma 6** Algorithm 2 satisfies wait-free recovery and wait-free exit.

*Proof* Since the recovery and exit sections do not contain any loops, it follows that in any history, any execution of **Recover()** and **Exit()** by a process  $p_i$  completes in a bounded number of  $p_i$ 's steps.

**Lemma 7** Algorithm 2 has worst-case RMR complexity O(1) per passage in the CC and DSM models.

**Proof** It suffices to prove that a process incurs O(1) RMRs at lines 15 and 17 because there are no other loops. The lemma follows easily in the DSM model since process  $p_i$  only spins on P[i], which is defined at initialization as local to  $p_i$ .

In the CC model the spin loops must be analyzed in greater detail to account for possible cache invalidations. The spin loops occur at lines 15 and 17, where  $p_i$  waits for  $P[i] \geq 1$  and P[i] = 2, respectively. A write operation on P[i] by another process  $p_j$  can only occur at lines 4, 14, or 21. If such a write occurs at line 14 or line 21 then it ensures that P[i] = 2, which holds until  $p_i$ 's next execution of line 9 by Lemma 4. As a result,  $p_i$ 's spin loop ends after one RMR to read P[i] = 2 into its local cache. On the other hand, if a write of P[i]by another process  $p_j$  occurs at line 14 then it ensures that  $P[i] \geq 1$ , which holds until  $p_i$ 's next execution of line 9 by Lemma 4. As a result, P[i] is not written at line 14 again until  $p_i$  executes line 9 due to the condition P[i] = 0 tested at line 13 and because the mutex is accessed by at most two processes at a time. Thus, line 14 contributes at most one RMR to any execution of a spin loop by  $p_i$ .

Process,  $p_i$  incurs at most two RMRs at line 15: one to read P[i] into its local cache, if P[i] is not already cached after line 15, and at most one due to a write at line 4, 14, or 21. Next,  $p_i$  incurs at most three RMRs at line 17: one to read P[i] into its local cache, if P[i] is not already cached after line 15, at most one due to line 14, and one more when  $p_i$  first reads P[i] = 2 due to a write at line 4 or 21.

**Theorem 1** Algorithm 2 satisfies ME, SF, WFR, and WFE. Furthermore, its worst-case RMR complexity per passage is O(1) in the CC and DSM models.

*Proof* Properties ME, SF, WFR, and WFE follow immediately from Lemmas 2, 5, and 6. The RMR complexity bound is established in Lemma 7.  $\Box$

# 3.2 Adding Bounded Critical Section Re-entry

A recoverable mutual exclusion algorithm can be augmented easily with the BCSR property using only O(N)additional shared variables and O(1) additional RMRs per passage in the CC and DSM models. Algorithm 3 presents a transformation that achieves this goal by tracking CS ownership using an array C[1..N] of bits. A process  $p_i$  assigns C[i] := 1 shortly before entering the CS at line 27, and resets this variable at line 28 shortly after clearing the CS. If  $p_i$  crashes in the CS, which implies C[i] = 1, then it bypasses the body of the recovery and entry sections in each subsequent passage until it re-enters the CS and reaches the exit section. We apply this transformation to the two-process algorithm from Section 3.1 before using it as a building block of an N-process algorithm in Section 3.3.

The analysis of Algorithm 3 is straightforward with the exception of one detail: the execution path following a failure in the CS omits the recovery and entry sections

| - $mtxB$ : base mutex, recoverable<br>- $C[1N]$ : array of integer, all elements initially zero | ) |

|-------------------------------------------------------------------------------------------------|---|

| <b>Procedure Recover()</b> for process $p_i$                                                    |   |

| if $C[i] = 0$ then                                                                              |   |

| $\int mtxB.\mathbf{Recover}()$                                                                  |   |

| <b>Procedure Enter()</b> for process $p_i$                                                      |   |

| $\mathbf{if} \ C[i] = 0 \ \mathbf{then}$                                                        |   |

| mtxB.Enter()                                                                                    |   |

| C[i] := 1                                                                                       |   |

\_\_\_\_\_

Shared variables:

**Procedure Exit()** for process  $p_i$

**28** C[i] := 0

**29**  $mtxB.\mathbf{Exit}()$

**Algorithm 3:** Transformation from recoverable base mutex to recoverable BCSR target mutex.

of mtxB, which goes against the sequential flow of control defined in our model (see Algorithm 1). We first justify this misuse of the base mutex in Lemma 8.

**Lemma 8** For any history H of Algorithm 3, let H' be the projection of H onto steps internal to mtxB, as well as all crash steps except where a process  $p_i$  fails while C[i] = 1 holds. Then H' is a history of the algorithm that implements mtxB.

*Proof* A process  $p_i$  executes the base recovery, entry, and exit sections in H' in the correct order for each passage of the target algorithm, as required, except when C[i] = 1 holds upon leaving the RS. The latter situation arises when a process  $p_i$  crashes after completing line 26 and before completing line 28. In that case  $p_i$ 's last access to mtxB is a call to **Enter**() at line 26, and its next access is either a call to **Exit**() if it reaches line 29 and does not crash after resetting C[i] at line 28, or a call to **Recover**() if it completes line 28 and crashes before calling **Exit**() at line 29. In the former case, the correct calling sequence with respect to Algorithm 1 is preserved since all crash steps by  $p_i$  occurring while C[i] = 1 are omitted from H'. In the latter case, the crash step is recorded in H' and  $p_i$  begins a new passage through mtxB, as required.

# **Theorem 2** Algorithm 3 satisfies BCSR.

**Proof** Suppose that a process  $p_i$  crashes in the CS of the target mutex. Then C[i] = 1 holds at the time of failure due to line 27, and so  $p_i$  completes the target recovery and entry sections in a bounded number of its own steps in each subsequent passage until it re-enters the target CS and then completes line 28.

**Theorem 3** Algorithm 3 preserves the following correctness properties of mtxB: ME, DF, SF, WFR, k-BR, TE, WFE, k-FCFS, and asymptotic worst-case RMR complexity per passage in the CC and DSM models.

Proof Let H be a history of Algorithm 3, and let H' be the projection defined in the statement of Lemma 8. We make the following observations: (i) H' is a history of mtxB by Lemma 8; (ii) if H is fair then H' is also fair; (iii) if a passage in H' is k-failure-concurrent then all passages in the corresponding super-passage through the target mutex in H are also k-failure-concurrent because H contains all the crash steps of H'. The correctness properties of mtxB are therefore preserved by the following arguments.

<u>ME</u>: The target CS is protected by mtxB.

<u>DF and SF</u>: The target algorithm has no loops, and so a process may be stuck on the way to the CS only inside the recovery or entry section of mtxB.

<u>WFR and k-BR</u>: These properties follow from the simple structure of the recovery section.

<u>TE and WFE</u>: These properties follow from the simple structure of the exit section. The target algorithm has no loops, and so a process may be stuck in  $\mathbf{Exit}()$  only if it is stuck inside  $mtxB.\mathbf{Exit}()$ .

<u>k-FCFS</u>: This property follows from the structure of the entry section assuming that the doorway of the target algorithm is defined as the code from the beginning of **Enter**() until the last step of the doorway of mtxB executed at line 26. Note that although the BCSR mechanism may disrupt the order of entry into the CS prescribed by mtxB, passages in which a process  $p_i$  bypasses the body of **Enter**() with C[i] = 1 are 0-failure-concurrent, and hence irrelevant to the definition of k-FCFS for all  $k \geq 0$ .

<u>RMR complexity</u>: Each passage through the target algorithm entails at most one execution of the base recovery, entry, and exit sections, as well as a constant number of additional steps. The transformation therefore introduces O(1) additional RMRs per passage in the worst case in the CC and DSM models.

# 3.3 An Algorithm for N Processes

Our N-process solution is modeled after Yang and Anderson's N-process algorithm [49], which is based on the arbitration tree of Kessels [33]. The algorithm is structured as a binary tree of height  $O(\log N)$  where each node is a two-process mutex implemented using the algorithm described in Section 3.1. Each process is mapped statically to a leaf node in the tree as follows: process  $p_i$  enters at leaf node number [i/2] counting from 1. Furthermore, side = left at leaf level if i is odd and side = right if i is even.

#### Shared variables:

A complete binary tree containing at least  $\lceil N/2 \rceil$ and fewer than N leaf nodes, numbered starting at 1, and where each node is an instance of Algorithm 2 from Section 3.1 augmented with BCSR using the transformation from Section 3.2.

**Procedure Recover()** for process  $p_i$

30 (empty)

Procedure Enter() for process  $p_i$ 31  $node := leaf node \lceil i/2 \rceil$ 32 if i is odd then 33  $\mid side := left$ 34 else

side := right35 while *node* is not the root do 36 37  $node. \mathbf{Recover}(side)$ node. Enter(side)38 39 if *node* is a left child then  $side := \mathsf{left}$ 40 else 41 side := right42 node := parent of node43

**Procedure Exit()** for process  $p_i$

44  $node := \bot$ 45 repeat 46 if  $node = \perp$  then node := root node47  $\mathbf{48}$ else node := child of node on the path to leaf49 node  $\lceil i/2 \rceil$ if node is a leaf and i is odd, or if leaf node  $\lfloor i/2 \rfloor$ 50 is in the left subtree of *node* then 51 side := left52 else | side := right 53  $node. \mathbf{Exit}(side)$ 54 until *node* is a leaf 55

**Algorithm 4:** Recoverable extension of Yang and Anderson's *N*-process mutex.

The recoverable N-process mutex is presented as Algorithm 4 for process  $p_i$ . Detailed pseudo-code is analogous to the non-recoverable N-process algorithm in [49] except that the two-process instances are implemented using our recoverable two-process mutex. The recovery section is empty since no additional recovery actions are required beyond those performed internally by the two-process mutex instances. The entry section entails executing the recovery and entry section (back to back) of each two-process mutex on the path from the designated leaf node of a process to the root, in that order. The exit section releases the two-process mutex instances in the opposite order, namely from root to leaf.

The remainder of this section presents the analysis of Algorithm 4. Theorem 4 asserts the main correctness properties: ME, SF, WFR, WFE, and  $O(\log N)$  worstcase RMR complexity in the CC and DSM models.

As the first step towards proving the correctness properties of the N-process mutex, we first establish that the two-process instances satisfy their safety properties when used inside Algorithm 4 (see Lemma 9). The safety properties of Algorithm 4 will then follow easily, and liveness (SF) will be established by a separate proof in Lemma 13.

**Lemma 9** For any finite history H of Algorithm 4, and for any two-process mutex instance  $M_2$  in the arbitration tree, let H' be the projection of H onto steps executed inside  $M_2$  as well as all crash steps. Then H'is a history of Algorithm 2 augmented with BCSR using Algorithm 3, and hence  $M_2$  satisfies its safety properties (ME, WFR, WFE, and RMR complexity) in H'.

*Proof* The safety properties of  $M_2$  in H' follow from Theorem 1 provided that H' is indeed a possible history of Algorithm 2. To that end, we must show that  $M_2$ is accessed correctly by processes, particularly that the following properties hold with respect to super-passages through  $M_2$ :

- 1. at most two processes at a time are executing a super-passage; and

- 2. if two processes at a time are executing a superpassage then they ascended to the tree node corresponding to  $M_2$  from distinct subtrees; and

- 3. the *side* parameter used by a process is fixed in any given super-passage; and

- 4. if two processes are executing super-passages concurrently then their *side* parameters are distinct.

The proof proceeds by induction on the height h of  $M_2$ above leaf level in Algorithm 4, which generates H. In the base case, h = 0, at most two processes are mapped statically to  $M_2$ , with one process (having the smaller ID) always accessing with side = left and the other always with side = right. Thus, clauses 1–4 follow immediately. Next, suppose for induction that the lemma holds for all two-process instances up to and including some height  $h \ge 0$ , and consider an instance  $M_2$  at height h + 1, if one exists.

<u>Clause 1 and 2:</u> Each process ascending to  $M_2$  from one of the subtrees occupies the critical section of a mutex at height h at the root of the subtree, and so it follows from the induction hypothesis, Theorem 1, and Theorem 3 that this critical section is executed in mutual exclusion. Thus, at most two processes at a time (one per subtree of  $M_2$ 's tree node) may be outside the RS of  $M_2$ . This observation and the BCSR property of the mutex at the root of the subtree (see Theorem 2) further ensure that at most two processes at a time (one per subtree) are executing a super-passage through  $M_2$ , as required.

<u>Clause 3:</u> Next, consider the *side* of a process  $p_i$  executing a super-passage through  $M_2$ . Since the path of nodes traversed by  $p_i$  through the arbitration tree is determined uniquely by i, it follows that  $p_i$  always accesses  $M_2$  with the same *side*: left if it ascends from the left subtree (see lines 40 and 51), and right if it ascends from the right subtree (see lines 42 and 53) of the corresponding tree node.

Clause 4: If processes  $p_i$  and  $p_j$  execute super-passages through  $M_2$  concurrently then they ascend from distinct subtrees by clause 2. In particular, if i < j, then  $p_i$  and  $p_j$  ascend to  $M_2$  from the left and right subtrees, respectively. As explained in the proof of clause 3, this implies that  $side_i = \text{left}$  and  $side_j = \text{right}$ . Thus,  $side_i \neq side_j$ .

# Lemma 10 Algorithm 4 satisfies mutual exclusion.

**Proof** A process enters the CS of Algorithm 4 only while it is in the CS of the two-process instance at the root node of the arbitration tree. This two-process instance satisfies mutual exclusion by Lemma 9.  $\Box$

# **Lemma 11** Algorithm 4 satisfies wait-free recovery and wait-free exit.

*Proof* The recovery section of Algorithm 4 is empty, and the exit section performs  $O(\log N)$  iterations of a loop that invokes the wait-free exit protocol of Algorithm 2 (see Theorem 1) with O(1) additional steps introduced by the BCSR transformation described in Algorithm 3 (see Theorem 3).

**Lemma 12** Algorithm 4 satisfies bounded critical section re-entry.

**Proof** Suppose that process  $p_i$  crashes inside the CS in some history H. We must show that  $p_i$  incurs a bounded number of steps in each subsequent execution of the recovery and entry sections until it re-enters the CS. The number of steps  $p_i$  incurs in **Recover**() is always zero, since Algorithm 4 has a trivial recovery section. The number of steps  $p_i$  incurs in each execution of **Enter**() is bounded until  $p_i$  re-enters the CS because in that case it is re-entering the CS of every two-process mutex on the bounded path from its designated leaf to the root (even if  $p_i$  crashes repeatedly), and each such execution of **Recover**() and **Enter**() of the two-process mutex incurs a bounded number of  $p_i$ 's steps by the BCSR property (see Theorem 2). Thus,  $p_i$  incurs a bounded number of steps in each subsequent execution of **Recover**() and **Enter**() of Algorithm 4 until it re-enters the CS, as required.

# Lemma 13 Algorithm 4 satisfies starvation-freedom.

*Proof* Let H be an infinite fair history of Algorithm 4 and suppose that H contains finitely many crash steps. Let  $p_i$  be a process that leaves the RS in H. We must show that  $p_i$  subsequently enters the CS. Suppose for contradiction that  $p_i$  does not, which implies that  $p_i$ never completes the super-passage through Algorithm 4 in which we suppose it leaves the RS. Then  $p_i$  takes infinitely many steps in H, and in particular it becomes stuck in some two-process mutex instance  $M_2$  in the arbitration tree, as otherwise it would eventually ascend to the CS of Algorithm 4. Let H' be the projection of H onto steps taken inside  $M_2$ . Then H' is a history of Algorithm 2 augmented with BCSR using Algorithm 3 by Lemma 9, and it contains finitely many crash steps because it is a subsequence of H. Since  $p_i$  is stuck forever in  $M_2$  in H, it also follows that H' is infinite as  $p_i$ is equally stuck in H'. To complete the proof, we will show that H' is fair, in which case  $p_i$ 's lack of progress in H' contradicts the SF property of  $M_2$  (see Theorem 1 and Theorem 3).

Consider any process  $p_j$  and suppose that  $p_j$  begins a super-passage through  $M_2$  by leaving the RS of  $M_2$  in H'. Since H' is infinite and contains finitely many crash steps, we must show that  $p_j$  continues to take steps in H' until it completes this super-passage through  $M_2$  or becomes stuck forever. This certainly holds if j = i since  $p_i$  becomes stuck in  $M_2$ , so consider  $j \neq i$ . Anytime  $p_j$ begins a passage through  $M_2$ , it either completes this passage, becomes stuck, or crashes. Thus, we must show that if  $p_i$  crashes then it eventually leaves the RS of  $M_2$ again, possibly after a finite number of additional crash steps, and resumes its ongoing super-passage. The corresponding crash step s in H causes  $p_i$  to transition from the recovery, entry or exit section to the RS with respect to Algorithm 4, and also from the CS to the RS with respect to every two-process mutex  $p_i$  has acquired during its traversal of the arbitration tree. On recovery,  $p_i$  leaves the RS of Algorithm 4, and until it re-enters the CS of Algorithm 4,  $p_i$  is able to complete **Recover**() and **Enter**() in a bounded number of steps by the BCSR property of the two-process mutex at each tree node (see Theorem 2) on the bounded path from  $p_i$ 's leaf to the root. Since H contains finitely many crash steps, this implies that eventually  $p_i$  ascends back to  $M_2$  without crashing, and hence leaves the RS of  $M_2$  in H', as required.

**Lemma 14** Algorithm 4 has worst-case RMR complexity  $O(\log N)$  per passage in the CC and DSM models.

*Proof* The lemma follows directly from Lemma 9, the constant worst-case RMR complexity per passage of Algorithm 2 (see Theorem 1), the worst-case RMR complexity preservation property of Algorithm 3 (see Theorem 3), and the logarithmic height of the arbitration tree.  $\hfill \Box$

**Theorem 4** Algorithm 4 satisfies ME, WFR, WFE, BCSR, and SF. Furthermore, its worst-case RMR complexity per passage is  $O(\log N)$  in the CC and DSM models.

*Proof* Properties ME, WFR, WFE, BCSR, and SF follow immediately from Lemmas 10, 11, 12, and 13. The RMR complexity bound is established in Lemma 14.

## 3.4 Discussion of Space Complexity

Burns and Lynch [10] proved a lower bound of  $\Omega(N)$ on the space complexity (i.e., the requirement of at least N shared variables) of deadlock-free mutual exclusion algorithms that use only reads and writes. Our Nprocess algorithm from Section 3.3 as well as Yang and Anderson's algorithm [49], on which ours is based, exceed this bound because they require one spin variable per process per level of the arbitration tree, for a total of  $\Theta(N \log N)$  shared variables. The space complexity of Yang and Anderson's algorithm can be reduced to  $\Theta(N)$  using a transformation proposed by Kim and Anderson [32]. It is not clear whether the same transformation works correctly for our recoverable algorithm because of the additional execution paths by which a recovering process may overwrite its rival's spin variable, namely at line 4 or at line 21 by way of line 6. In the CC model, our two-process algorithm can be simplified similarly to Yang and Anderson's so that only two spin variables are required per instance, which reduces the space complexity of the N-process solution to  $\Theta(N)$ .

# **4** General Solutions

In this section we develop recoverable mutual exclusion algorithms that improve on the N-process solution from Section 3 in terms of RMRs in the absence of failures. Such algorithms necessarily require synchronization primitives other than atomic reads, writes, and

Compare-And-Swap (CAS), as otherwise they are subject to the lower bound of  $\Omega(\log N)$  for worst-case RMR complexity per passage [6]. In asynchronous failure-free models, the best known solutions in terms of RMRs are queue locks [4] such as Mellor-Crummey and Scott's algorithm (MCS) [39], which has O(1) RMR complexity in the CC and DSM models, and uses both CAS and Fetch-And-Store (FAS) in addition to atomic reads and writes.

The high-level idea underlying our constructions in this section is to augment an ordinary mutex with a recovery procedure that restores the internal structure of the lock, such as the process queue in MCS, in the event of a failure. To our knowledge, the recoverable MCS lock of Bohannon, Lieuwen, and Silberschatz [8] was the first to follow this approach. Their solution makes two assumptions: crash failures are permanent and detectable by the operating system, and the recovery section is executed in a single dedicated process that is itself reliable. That is, the operating system invokes the recovery code automatically when a failure occurs, and there is no need to synchronize multiple processes recovering in parallel. Their algorithm achieves O(1)RMR complexity per passage in the CC and DSM models, but only when the passage does not overlap with the execution of the recovery process, and does not require any synchronization primitives beyond those used in MCS.

Our initial attempt to generalize the approach of Bohannon, Lieuwen, and Silberschatz to crash-recovery failures [45] led to an algorithm that has O(1) RMR complexity in the CC and DSM models in a failure-free passage and  $\Theta(N)$  RMRs in the worst case, but requires a powerful Fetch-And-Store-And-Store (FASAS) primitive that is not supported by modern multiprocessors except through transactional memory. Note that [8] and [45] both require  $\Omega(N)$  RMRs in the worst case to execute the recovery section alone (ignoring the cost of interacting with the operating system to detect failures in [8]) due to some form of interaction with every other process. In [8], this entails checking if the other processes are attempting to acquire the lock, and in [45], it entails traversing the queue structure to test whether the recovering process is already in it. In comparison, the composition of our constructions in Sections 4.1 and 4.2 transforms the MCS lock (among other algorithms) into a recoverable mutex that incurs O(1) RMRs in the DSM and CC models in a passage that is not 2-failureconcurrent, O(N) RMRs in the DSM and CC models per passage in the worst case, and uses only widelysupported synchronization primitives.

# 4.1 Transformation for Recoverability

Our first construction, presented in Algorithm 5, is a general transformation of ordinary mutex algorithms (base algorithms) into recoverable ones (target algorithms), and therefore operates in a fundamentally different way from the recoverable MCS locks discussed earlier. Specifically, our construction is agnostic with regard to the internal structure of the base algorithm in that we deal with failures by resetting the base algorithm to its initial state, rather than by attempting delicate repairs. We assume that the base mutex algorithm provides a procedure **Reset**() for this purpose that can be executed by any process as long as no other process is accessing the base mutex concurrently. For example, this method can loop over the objects internal to the base mutex and overwrite each with its initial value.

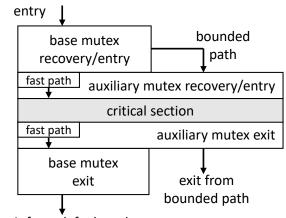

Resetting the base mutex is a disruptive action that requires careful synchronization between processes executing the recovery section (i.e., processes in cleanup) and other processes that may be accessing the base algorithm. We simplify this task by protecting the core of the recovery section using an auxiliary recoverable mutex, namely the one described in Section 3.3, which incurs additional RMRs for a process in cleanup but does not affect the RMR complexity in the absence of failures. In the critical section of the auxiliary mutex, the process in cleanup first "breaks" the base mutex in a manner that allows other processes to leave the base entry and exit sections in a bounded number of their own steps. It then waits for every other process to either arrive at a gating mechanism that prevents further access to the base mutex, or to crash and recover, in both cases raising a signal by writing a spin variable. Finally, the process in cleanup resets the base mutex, opens the gate, and releases the auxiliary mutex.

Algorithm 5 uses an array C[1..N] of integer variables to record the progress of each process in a superpassage, similarly to the way Algorithm 2 embeds integer tags into elements of its own array C. In the absence of failures, a process executing the target mutex bypasses the recovery section at line 56, executes the body of the target entry section where it acquires the base mutex at line 79, completes the critical section, and finally releases the base mutex in the target exit section at line 82. If a failure occurs, the execution path is steered carefully using the gating mechanism, which is implemented using an array Gate[1..N] of spin variables. The gate is controlled in the core of the recovery section at lines 63-70, which are protected by mtxA, the recoverable auxiliary mutex. A process in cleanup first closes the gate at line 63, and then reopens it at

line 69. The base mutex is reinitialized at line 68, which is only executed while the gate is closed.

One of the technical challenges in implementing the recovery section of the target algorithm is to suspend access to the base mutex, denoted mtxB, without sacrificing liveness. Consider for example the problematic scenario where process  $p_1$  waits inside mtxB.**Enter**() for process  $p_2$  to release mtxB, then  $p_2$  crashes, closes the gate while in cleanup, and waits for  $p_1$  to release mtxB so that it can be reset safely. To prevent deadlock, executions of mtxB.Enter() at line 79 and base exit section at line 82 are modified as follows: process  $p_i$  repeatedly checks Gate[i] while accessing mtxB, and returns immediately to the target entry or exit section if it observes  $Gate[i] \neq \bot$ , meaning that the gate is closed. In this context, "repeatedly checks" means that  $p_i$  reads Gate[i] after executing each step of the base mutex code (or at least after each step of a busy-wait loop). Thus, when the gate is closed by a process in cleanup,  $p_i$  is able to leave the base mutex code in a bounded number of its own steps, allowing the recovery section to make progress.

The recovery section only deals with crash failures that occurred outside the RS and CS, excluding crashes at lines 72–76 of the entry section. These scenarios are detected at line 56, including cases where recovery itself was interrupted by a crash. After assigning C[i] := 4 at line 57, process  $p_i$  reads Gate[i] at line 58 to determine whether the gate is already closed, either by  $p_i$  itself prior to failure or by another process in cleanup. If it is closed, then Gate[i] holds the ID of the process in cleanup, and  $p_i$  signals this process at line 60. This step is required to prevent deadlock, as explained earlier, if  $p_i$  crashed while holding the base mutex. Next,  $p_i$ acquires the auxiliary mutex at lines 61–62, closes the gate at line 63, waits at lines 64–67 for other processes to drain out of the base mutex code, resets mtxB at line 68, opens the gate at line 69, and finally releases the auxiliary mutex at line 70.

In the target entry section, process  $p_i$  first assigns C[i] := 1 at line 72, then checks whether the gate is closed at lines 73–74, and waits at line 76 until the gate is opened, if required. Prior to busy-waiting,  $p_i$  signals the process in cleanup at line 75 to prevent deadlock. When the gate is released,  $p_i$  updates its status by assigning C[i] := 2 at line 77 and then checks the gate again at line 78. If the gate is once again closed,  $p_i$  must restart the entry section to ensure that it does not access mtxB at line 79 concurrently with a process in cleanup. Note that checking the gate earlier at line 73 does not suffice for this purpose because at that point  $p_i$  has a different status (i.e., C[i] = 1 then vs. C[i] = 2 now), which is inspected in the recovery section

Shared variables:

- mtxA: auxiliary mutex implemented using Algorithm 4 from Section 3.3

- -mtxB: base mutex

- C[1..N]: array of integer, element C[i] local to

- process  $p_i$  in the DSM model, initially zero

- P[1..N][1..N]: array of Boolean, elements P[i][1..N] local to process p<sub>i</sub> in the DSM model, initially false

Gate[1..N]: array of proc. ID or ⊥, element Gate[i]

- local to process  $p_i$  in DSM model, initially  $\perp$

#### **Procedure Recover()** for process $p_i$

```

if C[i] \notin \{0,1\} then

56

57

C[i] := 4

// signal process in cleanup

incleanup := Gate[i]

58

if incleanup \neq \bot then

59

P[incleanup][i] := true

60

// clean up the base mutex

mtxA.\mathbf{Recover}()

61

mtxA.Enter()

62

// close the gate

63

for z \in 1..N do Gate[z] := i

// wait for processes to clear base mutex

for z \in 1..N do

64

65

P[i][z] := false

if z \neq i \land C[z] \in \{2,3\} then

66

await P[i][z] = true

67

68

mtxB.\mathbf{Reset}()

// reopen the gate

for z \in 1..N do Gate[z] := \bot

69

70

mtxA.\mathbf{Exit}()

C[i] := 0

71

```

**Procedure Enter()** for process  $p_i$

| 72        | C[i] := 1                                                  |

|-----------|------------------------------------------------------------|

|           | // wait at gate if needed                                  |

| 73        | incleanup := Gate[i]                                       |

| <b>74</b> | if $incleanup \neq \bot$ then                              |

|           | <pre>// signal process in cleanup</pre>                    |

| 75        | P[incleanup][i] := true                                    |

|           | <pre>// wait for gate to reopen</pre>                      |

| 76        | <b>await</b> $Gate[i] = \bot$                              |

| 77        | C[i] := 2                                                  |

| 78        | if $Gate[i] \neq \bot$ then goto line 72                   |

| 79        | execute steps of $mtxB$ . <b>Enter</b> () interleaved with |

|           | reads of $Gate[i]$ until done or $Gate[i] \neq \bot$       |

| 80        | if $Gate[i] \neq \bot$ then goto line 72                   |

|           | <b>Procedure Exit()</b> for process $p_i$                  |

|           |                                                            |

**81** C[i] := 3

s2 execute steps of mtxB.Exit() interleaved with reads of Gate[i] until done or Gate[i] ≠ ⊥

s3 C[i] := 0

// signal process in cleanup

s4 incleanup = Gate[i]

s5 if incleanup ≠ ⊥ then

s6 ∟ P[incleanup][i] := true

**Algorithm 5:** Transformation from *N*-process base mutex to *N*-process recoverable target mutex.

at line 66. On the other hand, if the gate is still open at line 78, then  $p_i$  executes mtxB.Enter() at line 79 until it either acquires the base critical section or detects that another process has closed the gate. The latter detection is accomplished by reading Gate[i] after each step of mtxB.Enter() at line 79. Upon executing mtxB.**Enter**() to completion, process  $p_i$  checks the gate yet again at line 80 and restarts the entry section of the target mutex if required, which prevents unsafe progress into the target critical section. As we show later on in Lemma 18, executing mtxB.Enter() repeatedly in the same passage through the target mutex is safe because in that scenario mtxB is reset between two consecutive calls to mtxB.**Enter**(). Once  $p_i$ enters and leaves the CS of the target mutex, it executes mtxB.**Exit()** at line 82 until it either succeeds or detects that another process has closed the gate. The gate is checked after each step of mtxB.Exit(), as in the earlier execution of mtxB.**Enter**(). Process  $p_i$  then checks the gate yet again at lines 84–85, and if the gate is closed,  $p_i$  signals the process in cleanup at line 86.

The remainder of this section presents the analysis of Algorithm 5. Theorem 5 asserts the main correctness properties, which include preservation of ME and SF with respect to the base algorithm, as well as preservation of RMR complexity in the absence of failures.